## COMPOSANTS ACTIFS DISCRETS 2

MICHEL GIRARD

EDISCIENCE international retronik fr 202

# COMPOSANTS ACTIFS DISCRETS

#### Dans la même collection

Electronique industrielle

Boucles à verrouillage de phase

Amplificateurs de puissance

Amplificateurs opérationnels 1

Amplificateurs opérationnels 2

Composants actifs discrets 1

### MICHEL GIRARD

Institut Universitaire de Technologie, Cachan Département Automatismes et Electronique de Puissance

# COMPOSANTS ACTIFS DISCRETS

2

Nous tenons à remercier les sociétés suivantes qui nous ont permis de reproduire certains schémas contenus dans cet ouvrage : ICT, National Semiconductor, Motorola, VTC, Harris-Intersil, Harris Semiconducteurs, Siliconix, Philips Composants, PMI.

Maquette de couverture : Françoise Rojare

© 1990, Ediscience international, Paris.

ISBN: 2-84074-069-9 ISSN: 0985-9039

(publié précédemment par McGraw-Hill Inc., Paris.

ISBN: 2-7042-1205-8)

La Loi du 11 mars 1957 n'autorisant, aux termes des alinéas 2 et 3 de l'Article 41, d'une part, que les «copies ou reproductions strictement réservées à l'usage privé du copiste et non destinées à une utilisation collective» et, d'autre part, que les analyses et les courtes citations dans un but d'exemple et d'illustration, «toute représentation ou reproduction intégrale, ou partielle, faite sans le consentement de l'auteur ou de ses ayants-droit ou ayants-cause, est illicite» (alinéa 1er de l'Article 40). Cette représentation ou reproduction, par quelque procédé que ce soit, constituerait donc une contrefaçon sanctionnée par les articles 425 et suivants du Code Pénal.

Ediscience international – 28, rue Beaunier – 75014 Paris

### **Avant-propos**

En 1989, un fabricant de circuits intégrés spécifiques à une application (ASIC) annonce : « L'expansion des ASIC mixtes – numériques, analogiques – est sérieusement freinée par le manque de concepteurs compétents en analogique : la fortune attend ceux qui choisissent, aujourd'hui, cette voie. »

Oui, la connaissance des composants discrets est obligatoire dans la pratique des techniques modernes (utilisation des circuits intégrés analogiques et numériques, simulation analogique en CAO, conception des circuits intégrés, etc.), mais elle est tout autant nécessaire pour l'étude des fonctions non intégrées telles que les circuits d'interface, les circuits de puissance, les circuits hautes fréquences... sans oublier les « petits montages rapides de dépannage ».

L'ouvrage *Composants actifs discrets* présente, d'abord quelques éléments de la physique des semiconducteurs nécessaires à l'étude du comportement des composants, puis les composants actifs discrets bipolaires et unipolaires (à effet de champ), et enfin l'intégration de ces composants. Une différence inévitable entre la théorie et la pratique est due aux imperfections de fabrication. Minimiser ces imperfections et améliorer les caractéristiques des composants représente « la science de l'art » des fabricants.

L'étude des composants discrets est d'abord qualitative, puis quantitative. L'ensemble est concrétisé par plus d'une centaine d'exercices entièrement traités.

Cet ouvrage s'adresse au très vaste public des étudiants post-baccalauréat (lycées, IUT, écoles d'ingénieurs, universités), des professeurs et des techniciens et ingénieurs de l'industrie.

Les chapitres peuvent être présentés succinctement.

#### Première partie (premier tome)

- Chapitre 1. Une présentation générale des méthodes d'étude est suivie d'une présentation des semiconducteurs et du comportement de la jonction PN.

- Chapitre 2. Toutes les diodes sont présentées, d'abord théoriquement, ensuite pratiquement, avec des exemples d'application.

- Chapitre 3. Ce chapitre est consacré au transistor bipolaire : étude qualitative, étude quantitative, fonctionnement idéalisé, amplificateurs continus et basses fréquences, puis amplificateurs hautes fréquences et micro-ondes.

#### Deuxième partie (deuxième tome)

- Chapitre 4. Il présente le transistor à effet de champ à jonction JFET et à grille isolée MOSFET, avec les mêmes rubriques que pour le transistor bipolaire (étude théorique, fonctionnement idéalisé, fonctionnement en interrupteur et en résistance commandée, amplificateurs continus et basses fréquences, amplificateurs hautes fréquences et micro-ondes).

- Chapitre 5. On y trouve les principes de la commutation faible puissance (bascules, etc.) et forte puissance (thyristor, triac, etc.).

- Chapitre 6. Ce chapitre présente la technologie des circuits intégrés analogiques bipolaires, BIFET, BIMOS, MOS et CMOS pour des fonctions classiques comme les amplificateurs opérationnels, les commutateurs analogiques, et moins classiques comme les circuits à capacités commutées.

- Chapitre 7. Les différentes technologies numériques y sont présentées (TTL, ECL, MOS, NMOS, CMOS, etc.) pour des fonctions à faible et forte intégration.

- Chapitre 8. C'est le sommet de la technologie intégrée avec l'apparition des ASIC pour différents degrés d'intégration à la demande, depuis les réseaux logiques programmables, jusqu'aux circuits spécifiques (full customs).

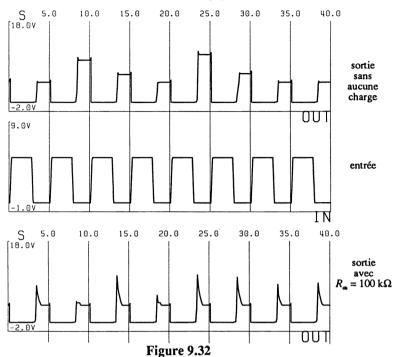

- Chapitre 9. Quelques éléments de CAO sont indiqués en simulation analogique avec des composants discrets classiques puis avec des composants intégrables dont les caractéristiques sont fournies par les fondeurs.

Remarque. Malgré nos efforts de relecture, le long travail de synthèse que représente cet ouvrage laissera inéluctablement apparaître des erreurs. Nous nous excusons auprès de nos lecteurs et les invitons à nous en faire part.

Je remercie vivement tous les collègues pour leurs conseils et informations et plus particulièrement Daniel Angélis responsable, entre autres, de la formation en CAO.

#### Conventions générales d'écriture

| V, I                                | tensions et courants continus                                                              |

|-------------------------------------|--------------------------------------------------------------------------------------------|

| <u>V</u> , <u>I</u>                 | tensions et courants sinusoïdaux, en notation complexe                                     |

| V(p), I(p)                          | tensions et courants en notation symbolique, variable de Laplace                           |

| v(t), i(t)                          | tensions et courants en régime quelconque, variable t                                      |

| + $V$ , – $V$ , + $E$               | tensions d'alimentation dans le cas général ou pour les cir-<br>cuits intégrés analogiques |

| + $V_{ m DD}$ – $V_{ m SS}$         | tensions d'alimentation dans le cas des circuits intégrés MOS                              |

| $v_{\rm E} = V_{\rm E} + v_{\rm e}$ | superposition des états statique et dynamique                                              |

| $V_{\rm CE}, I_{\rm C}, I_{ m CBO}$ | tensions et courants continus pour un composant                                            |

| $V_{\mathrm{CE}_0}, I_{\mathrm{C}_0}, \dots$ | tensions et courants de repos que l'on s'impose (point de repos) |

|----------------------------------------------|------------------------------------------------------------------|

| $v_{\rm ce}, i_{\rm c}, v_{ m be}, \dots$    | tensions et courants variables, autour d'une composante continue |

| β                                            | gain en courant d'un transistor bipolaire                        |

|                                              | $\beta=h_{21}=h_{\rm f}$                                         |

| 8                                            | transconductance d'un transistor                                 |

|                                              | $g = g_{\rm f}$                                                  |

| $\theta_{ m j}$ , $T_{ m j}$                 | température (dans notre cas, de jonction)                        |

## Table des matières

| Cha  | pitre 4 | l. Transi  | stors à effet de champ                                   | 1  |

|------|---------|------------|----------------------------------------------------------|----|

| 4.1. | Préser  | ntation, p | rincipe, théorie des transistors à effet de champ        | 1  |

|      | 4.1.1.  | Idée dire  | ectrice, principes simplifiés, domaines d'application    | 1  |

|      |         | 4.1.1.1.   | Conduction dans un barreau semiconducteur                | 1  |

|      |         | 4.1.1.2.   | Classification des transistors à effet de champ          | 2  |

|      |         | 4.1.1.3.   | Symbolisation                                            | 3  |

|      |         | 4.1.1.4.   | Domaines d'application des transistors à effet de champ  | 5  |

|      | 4.1.2.  |            | ors à jonction                                           | 7  |

|      |         | 4.1.2.1.   | Jonction PN                                              | 7  |

|      |         |            | Étude qualitative du transistor à jonction JFET canal N  | 8  |

|      |         |            | Étude quantitative du transistor à jonction JFET canal N | 12 |

|      |         |            | Relations simplifiées associées au transistor JFET       | 15 |

|      | 4.1.3.  |            | ors à grille isolée MOSFET                               | 16 |

|      |         |            | Condensateur métal-oxyde-semiconducteur                  | 17 |

|      |         |            | Étude qualitative du transistor NMOS à enrichissement    | 24 |

|      |         | 4.1.3.3.   | Étude qualitative du transistor NMOS à appauvris-        |    |

|      |         |            | sement                                                   | 28 |

|      |         |            | Étude quantitative des MOSFET, relations simplifiées     | 31 |

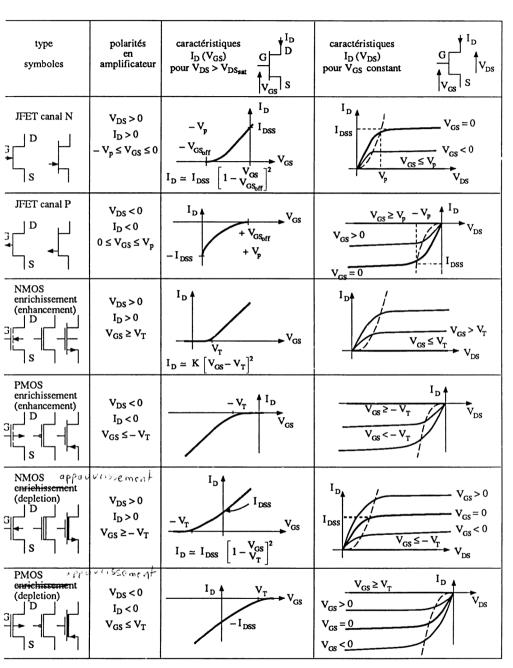

|      |         |            | des caractéristiques des transistors à effet de champ    | 34 |

|      | 4.1.5.  | Exercice   | es                                                       | 34 |

| 4.2. | Aspec   | t technolo | ogique des transistors à effet de champ                  | 43 |

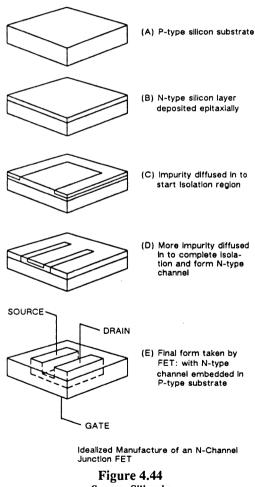

|      | 4.2.1.  | Fabricat   | ion des FET                                              | 43 |

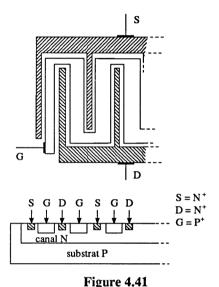

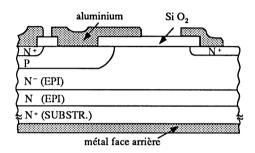

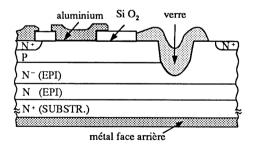

|      |         |            | Transistor à jonction JFET canal N                       | 43 |

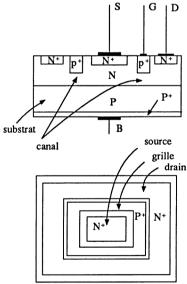

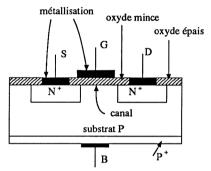

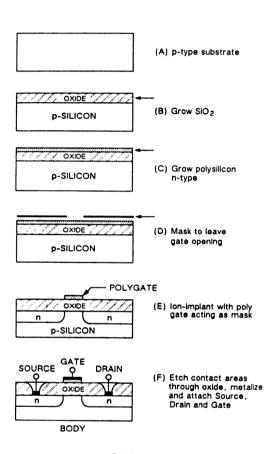

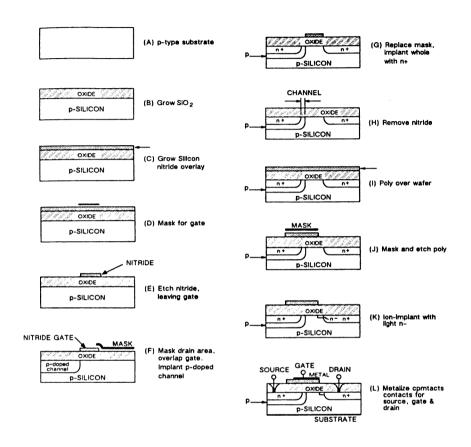

|      |         | 4.2.1.2.   | Transistors NMOS                                         | 44 |

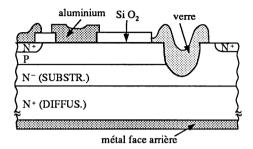

|      |         | 4.2.1.3.   | Exemples de procédés de fabrication et de géométries     |    |

|      |         |            | réelles                                                  | 46 |

|      | 4.2.2.  |            | istiques statiques réelles                               | 49 |

|      |         |            | Caractéristiques statiques du JET canal N                | 50 |

|      |         |            | Caractéristiques statiques des NMOS                      | 56 |

|      | 4.2.3.  |            | e de la température                                      | 60 |

|      |         |            | Variation des paramètres du JFET canal N                 | 60 |

|      |         | 4.2.3.2.   | Variation des paramètres des transistors NMOS            | 62 |

|      |        | 4.2.3.3. Résistance thermique – limitation de puissance      | 64     |

|------|--------|--------------------------------------------------------------|--------|

|      | 4.2.4. |                                                              | 64     |

|      |        |                                                              | 65     |

|      |        | 4.2.4.2. Transistors NMOS                                    | 65     |

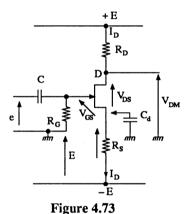

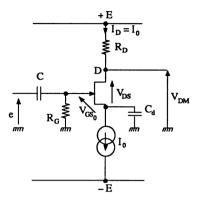

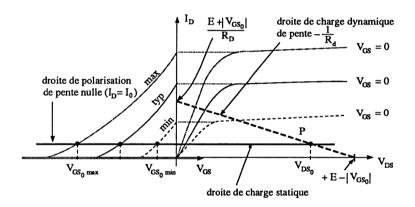

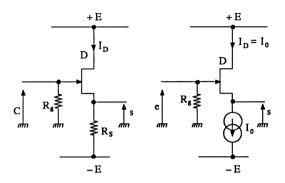

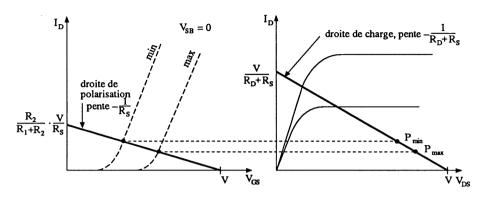

|      | 4.2.5. | Point de repos et polarisation                               | 66     |

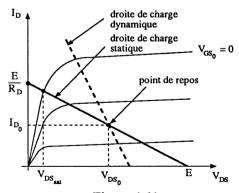

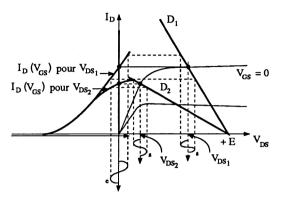

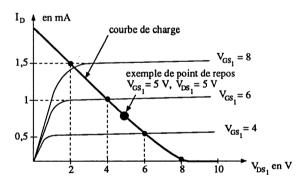

|      |        | 4.2.5.1. Droites de charges statique et dynamique            | 66     |

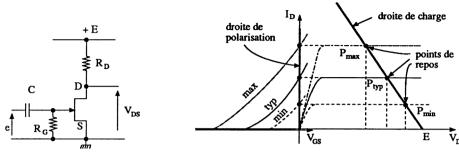

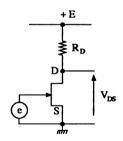

|      |        | 4.2.5.2. Polarisation des transistors à effet de champ       | 67     |

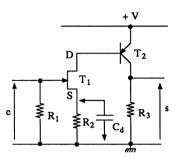

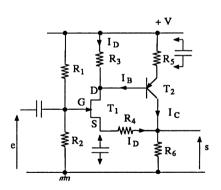

|      | 4.2.6. | Association de transistors FET et bipolaires                 | 77     |

|      | 4.2.7. | Transistors à effet de champ spéciaux                        | 79     |

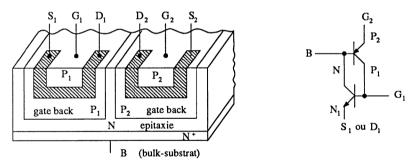

|      |        | 4.2.7.1. Transistors JFET pour amplificateurs différentiels  | 79     |

|      |        |                                                              | 79     |

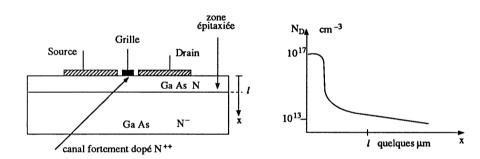

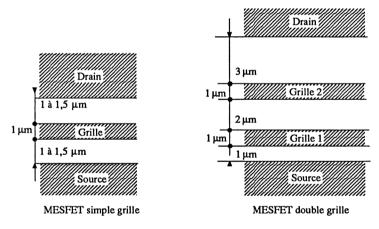

|      |        | 4.2.7.3. Transistors MESFET                                  | 80     |

|      |        | 4.2.7.4. Transistors à effet de champ à double grille        | 81     |

|      |        |                                                              | 82     |

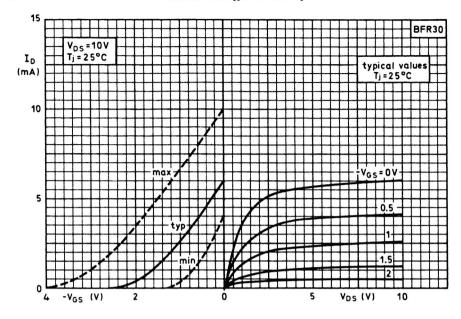

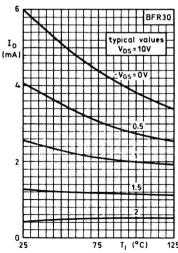

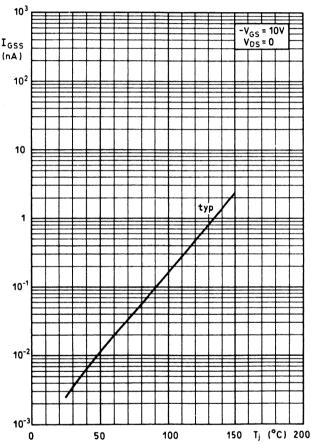

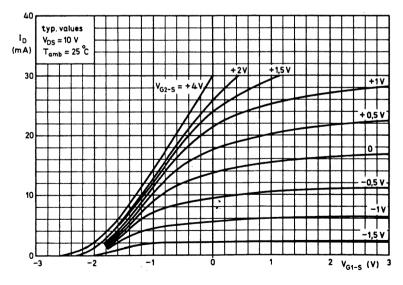

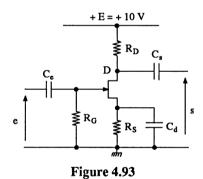

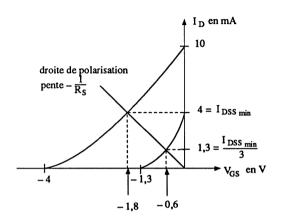

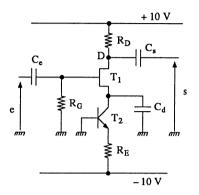

|      | 4.2.8. | Exemples de caractéristiques                                 | 82     |

| 4.3. | Applio | cations quasi statiques des transistors à effet de champ     | 95     |

|      |        |                                                              | 95     |

|      |        |                                                              | 96     |

|      |        |                                                              | 97     |

|      |        |                                                              | 99     |

|      | 4.3.2. |                                                              | 00     |

|      |        | <u> </u>                                                     | 01     |

|      |        |                                                              | 02     |

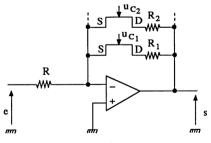

|      | 4.3.3. | Fonctionnement en résistance commandée                       | 02     |

|      |        | 4.3.3.1. Exemples d'application                              | 03     |

|      |        |                                                              | 05     |

|      |        |                                                              | 07     |

|      | 4.3.4. |                                                              | 09     |

| 4 4  | Ampli  | ificateurs continus et basses fréquences 1                   | 13     |

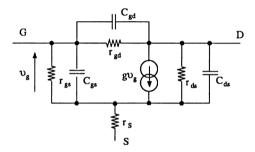

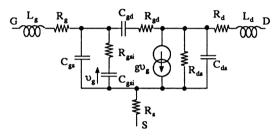

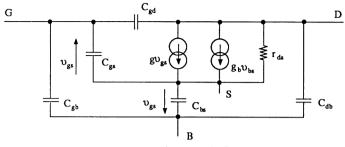

| •••• |        | Schémas équivalents du transistor à effet de champ en régime |        |

|      |        |                                                              | 13     |

|      |        |                                                              | 13     |

|      |        |                                                              | 13     |

|      |        | •                                                            | 15     |

|      | 4.4.2. |                                                              | 18     |

|      |        | <u>U</u>                                                     | 18     |

|      |        |                                                              | 20     |

|      |        |                                                              | 21     |

|      |        |                                                              | 22     |

|      |        |                                                              | <br>24 |

|      |        |                                                              | 25     |

|      |        |                                                              | 27     |

|      | 4.4.3. |                                                              | <br>28 |

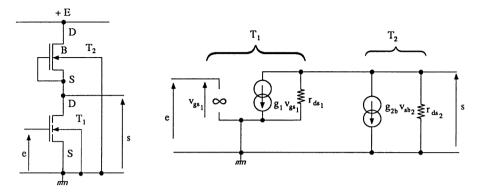

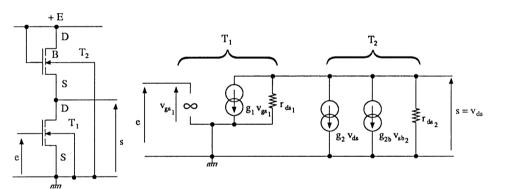

|      |        | 4.4.3.1.  | Charges actives                                          | 128 |

|------|--------|-----------|----------------------------------------------------------|-----|

|      |        | 4.4.3.2.  | Technologie JFET                                         | 130 |

|      |        | 4.4.3.3.  | Technologie MOS                                          | 131 |

|      |        |           | Influence de la tension substrat source                  | 134 |

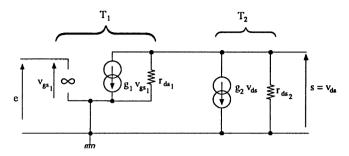

|      | 4.4.4. | Associat  | ion transistors FET-transistors bipolaires               | 135 |

|      |        | 4.4.4.1.  | Mise en cascade simple                                   | 136 |

|      |        | 4.4.4.2.  | Contre-réactions partielles                              | 137 |

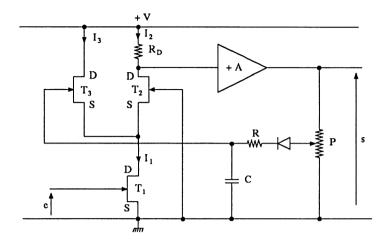

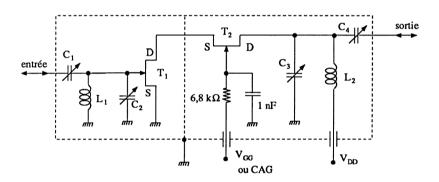

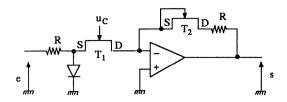

|      | 4.4.5. | Contrôle  | automatique de gain                                      | 139 |

|      |        | 4.4.5.1.  | CAG d'un montage source commune                          | 139 |

|      |        | 4.4.5.2.  | CAG d'un montage à amplificateur opérationnel            | 141 |

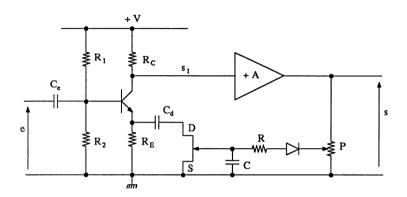

|      |        | 4.4.5.3.  | CAG d'un montage émetteur commun                         | 142 |

|      |        |           | CAG d'un montage cascode                                 | 142 |

|      | 4.4.6. | Imperfec  | ctions des amplificateurs continus et basses fréquences. | 143 |

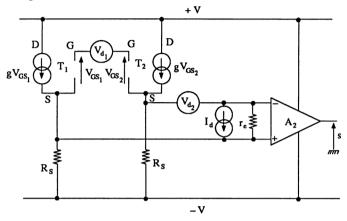

|      |        |           | Imperfections statiques                                  | 143 |

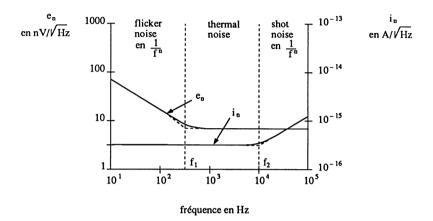

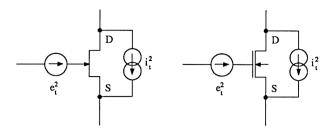

|      |        | 4.4.6.2.  | Bruit dans les transistors à effet de champ              | 149 |

|      |        |           | Distorsion dans les montages                             | 151 |

|      |        |           | Phénomène de latch-up dans les JFET « dual »             | 152 |

|      | 4.4.7. | Exercice  | es                                                       | 152 |

| 4.5. | Ampli  | ficateurs | vidéofréquences, radiofréquences et hyperfréquences      | 172 |

|      | -      |           | ors à effet de champ hautes fréquences                   | 172 |

|      |        | 4.5.1.1.  | Technologies utilisées                                   | 172 |

|      |        |           | Paramètres naturels du JFET                              | 172 |

|      |        | 4.5.1.3.  | Paramètres naturels du MESFET                            | 175 |

|      |        | 4.5.1.4.  | Paramètres naturels du MOSFET                            | 175 |

|      |        | 4.5.1.5.  | Schéma équivalent en paramètres y                        | 177 |

|      |        | 4.5.1.6.  | Schéma équivalent en paramètres s                        | 178 |

|      | 4.5.2. | Amplific  | cateurs vidéofréquences                                  | 180 |

|      |        |           | Impédance d'entrée d'un JFET                             | 180 |

|      |        | 4.5.2.2.  | Structures de base, pour amplificateurs vidéofréquences  | 181 |

|      |        | 4.5.2.3.  | Exemples de réalisations                                 | 182 |

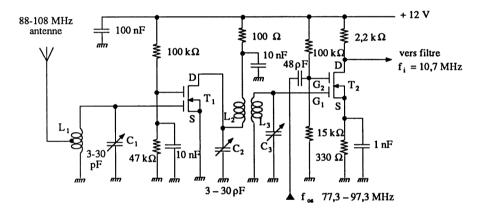

|      | 4.5.3. | Amplific  | cateurs radiofréquences                                  | 185 |

|      |        | 4.5.3.1.  | Structures de base pour amplificateurs radiofréquences   | 185 |

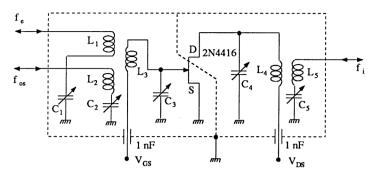

|      |        | 4.5.3.2.  | Détection, mélange de fréquences et multiplication de    |     |

|      |        |           | fréquences                                               | 188 |

|      |        | 4.5.3.3.  | Utilisation des transistors à effet de champ double      |     |

|      |        |           | grille TECDG                                             | 189 |

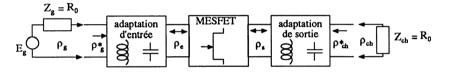

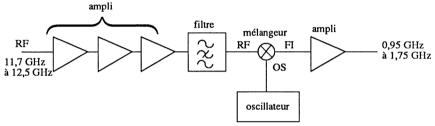

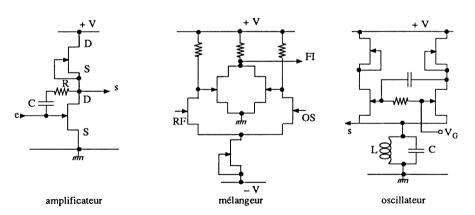

|      | 4.5.4. |           | cateurs micro-ondes                                      | 191 |

|      |        |           | Amplificateur adapté simple                              | 191 |

|      |        |           | Amplificateur à contre-réaction résistive                | 192 |

|      |        |           | Amplificateur équilibré                                  | 193 |

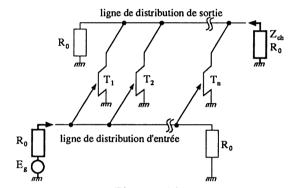

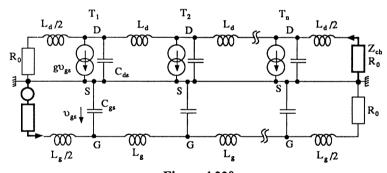

|      |        |           | Amplificateur distribué                                  | 193 |

|      | 4.5.5. | Exercice  | S                                                        | 195 |

|      |        |           | itation faible et forte puissance                     | 201 |

|------|--------|-----------|-------------------------------------------------------|-----|

| 5.1. |        |           | ple puissance en commutation                          | 201 |

|      | 5.1.1. | Diodes er | n commutation                                         | 201 |

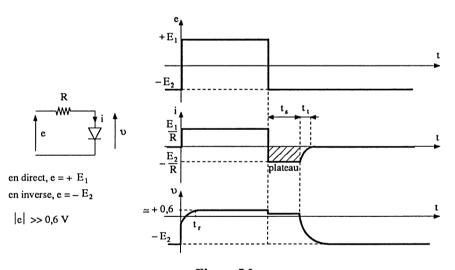

|      |        | 5.1.1.1.  | Diode normale en petits signaux                       | 202 |

|      |        | 5.1.1.2.  | Diode normale en grands signaux                       | 203 |

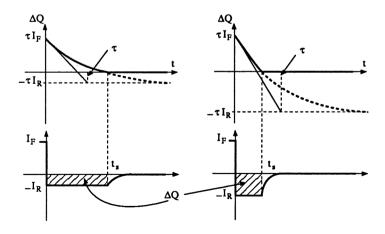

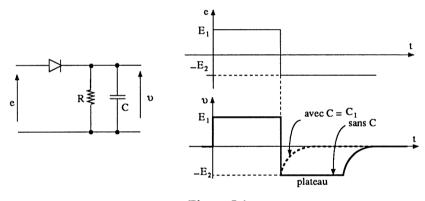

|      |        | 5.1.1.3.  | Diminution du temps de stockage dans les diodes       | 204 |

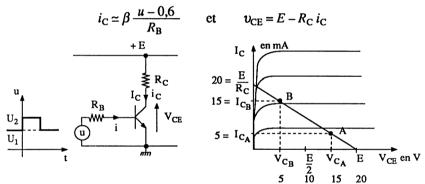

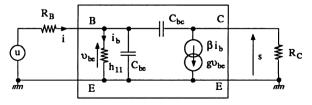

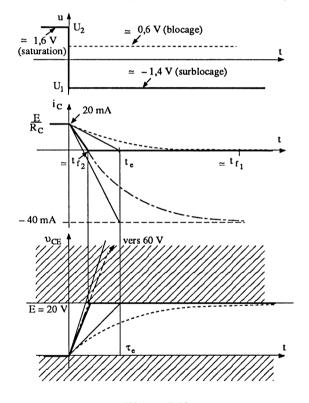

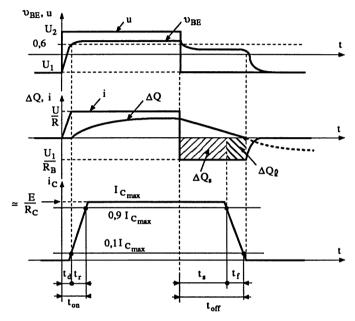

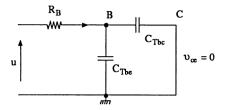

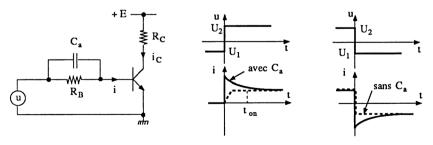

|      | 5.1.2. | Transisto | rs bipolaires en commutation                          | 206 |

|      |        |           | Transistors bipolaires en petits signaux              | 206 |

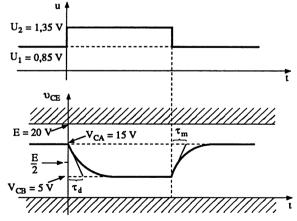

|      |        | 5.1.2.2.  | Transistors bipolaires en grands signaux              | 208 |

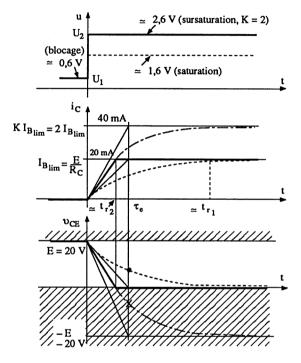

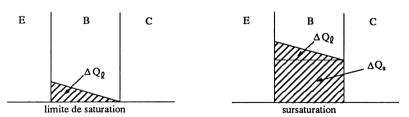

|      |        | 5.1.2.3.  | Fonctionnement en sursaturation et surblocage         | 210 |

|      |        | 5.1.2.4.  | Amélioration des temps de commutation du transistor   |     |

|      |        |           | bipolaire                                             | 214 |

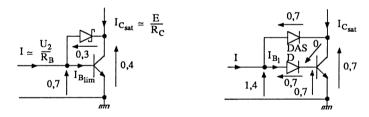

|      |        | 5.1.2.4.  | Puissance dissipée dans un transistor en commutation. | 216 |

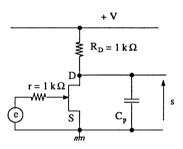

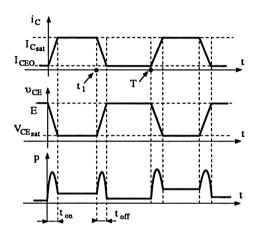

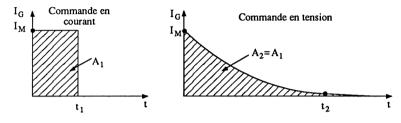

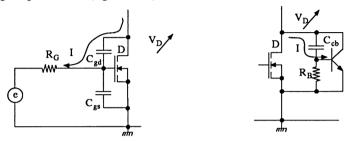

|      | 5.1.3. | Transisto | rs à effet de champ en commutation                    | 217 |

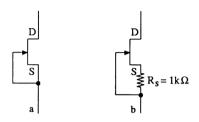

|      |        | 5.1.3.1.  | Transistor JFET en petits signaux                     | 217 |

|      |        | 5.1.3.2.  | Transistor JFET en grands signaux                     | 218 |

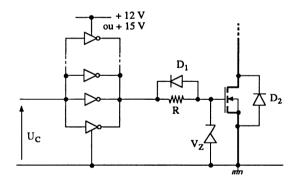

|      |        | 5.1.3.3.  | Cas des transistors MOSFET                            | 221 |

|      |        | 5.1.3.4.  | Exemples de valeurs et amélioration des temps de      |     |

|      |        |           | commutation                                           | 223 |

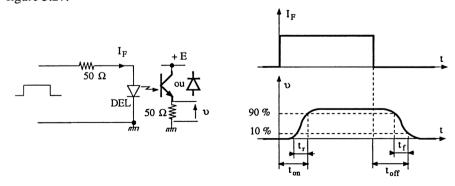

|      | 5.1.4. | Composa   | ints de l'optoélectronique en commutation             | 225 |

|      |        | 5.1.4.1.  | Émetteurs de lumière                                  | 225 |

|      |        | 5.1.4.2.  | Récepteurs de lumière                                 | 226 |

|      |        | 5.1.4.3.  | Optoisolateurs                                        | 227 |

| 5.2. | Applic | ations de | la commutation faible puissance                       | 228 |

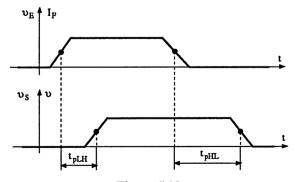

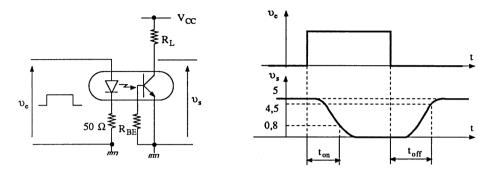

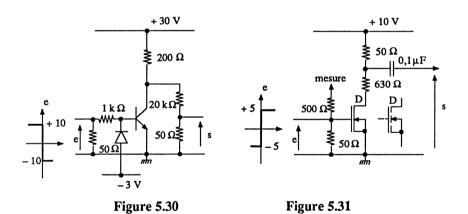

|      | 5.2.1. | Quelques  | schémas tests                                         | 229 |

|      | 5.2.2. | Exemples  | s de drivers pour transistors                         | 230 |

|      |        | 5.2.2.1.  | Driver à transistors bipolaires                       | 230 |

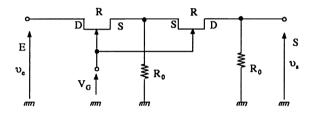

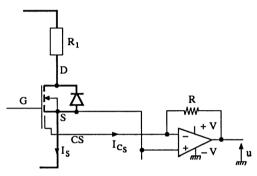

|      |        | 5.2.2.2.  | Drivers à transistors à effet de champ                | 230 |

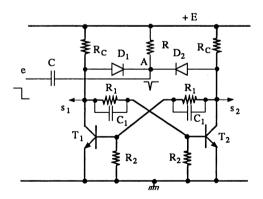

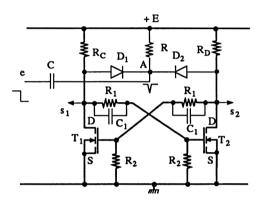

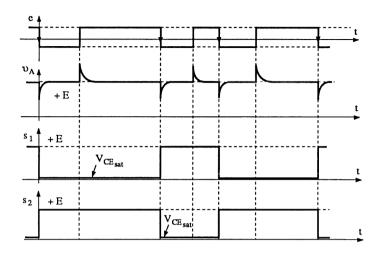

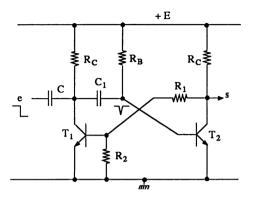

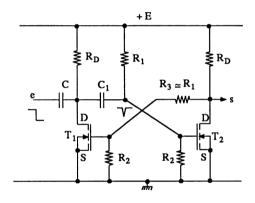

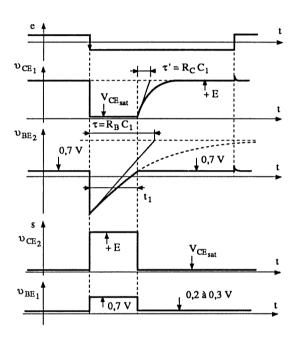

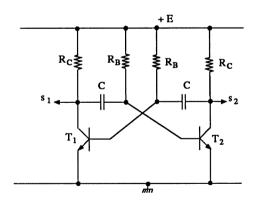

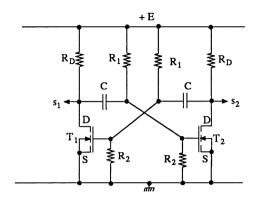

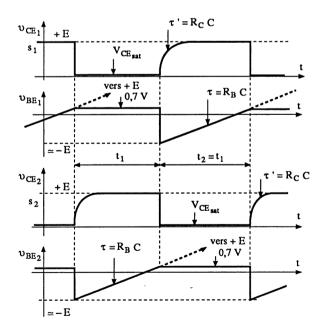

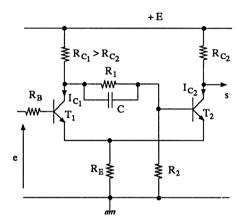

|      | 5.2.3. | Bascules  | à transistors                                         | 233 |

|      |        | 5.2.3.1.  | Bascules bistables                                    | 233 |

|      |        | 5.2.3.2.  | Bascules monostables                                  | 235 |

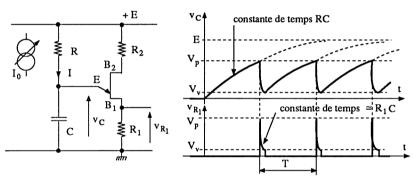

|      |        | 5.2.3.3.  | Bascules astables                                     | 238 |

|      |        | 5.2.3.4.  | Trigger de Schmitt                                    | 240 |

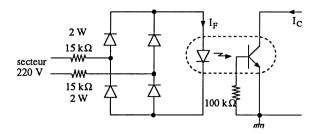

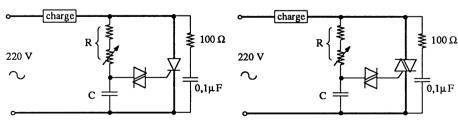

|      | 5.2.4. |           | s d'utilisation des optocoupleurs                     | 242 |

|      |        | 5.2.4.1.  | Optocoupleur diode-transistor bipolaire               | 242 |

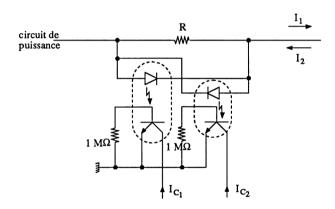

|      |        |           | Optocoupleur diode-JFET                               | 243 |

| 5.3. | Les co | mposants  | de puissance en commutation                           | 244 |

|      | 5.3.1. | Composa   | ints « linéaires » en commutation                     | 244 |

|      |        | 5.3.1.1.  | Diodes                                                | 244 |

|      |        |           | Transistors bipolaires                                | 245 |

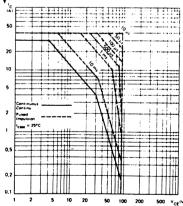

|      |        |           | Transistors à effet de champ                          | 248 |

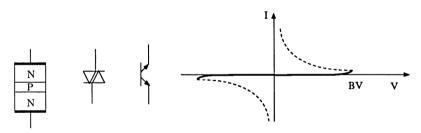

|      | 5.3.2. |           | nts à avalanche                                       | 252 |

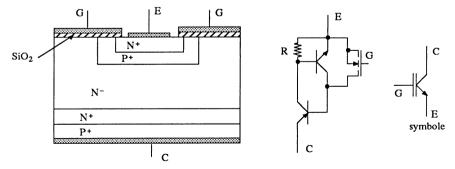

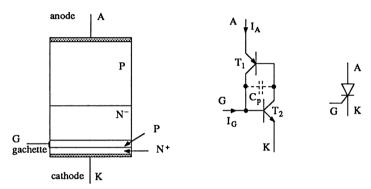

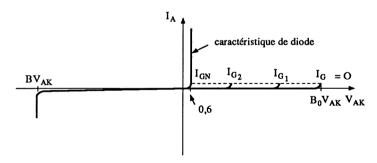

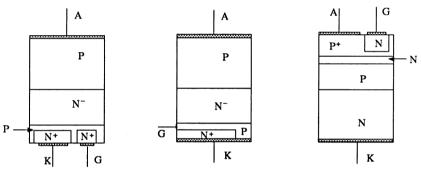

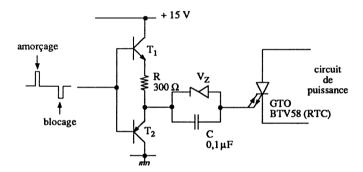

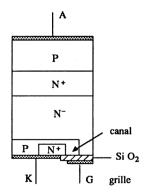

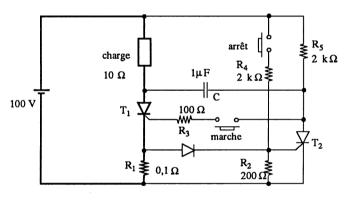

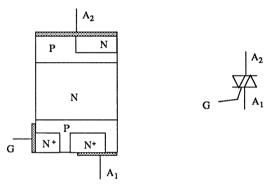

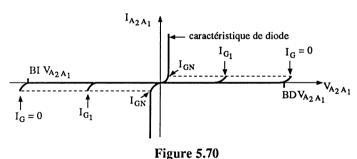

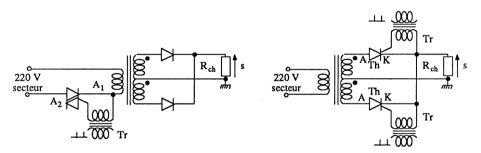

|      |        | •         | Thyristors                                            | 252 |

|            |          | 5.3.2.2. Triac                                               | 258<br>259 |

|------------|----------|--------------------------------------------------------------|------------|

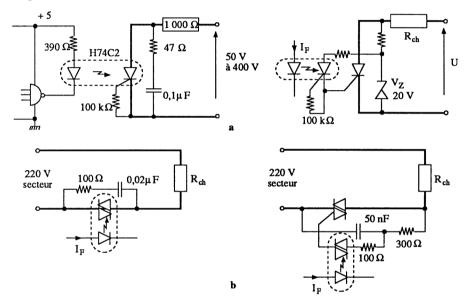

| 5.4.       |          | osants à avalanche de faible puissance                       | 260        |

|            |          | Thyristor tétrode                                            | 261        |

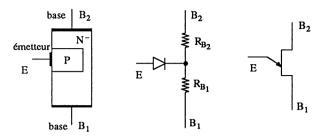

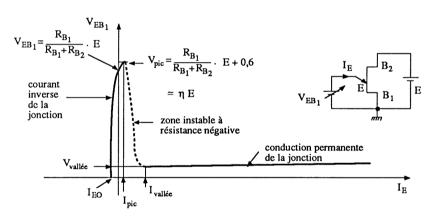

|            | 5.4.2.   | Transistor unijonction                                       | 261        |

|            |          | Transistor unijonction programmable                          | 264        |

|            | 5.4.4.   | Dipôles actifs à avalanche                                   | 265        |

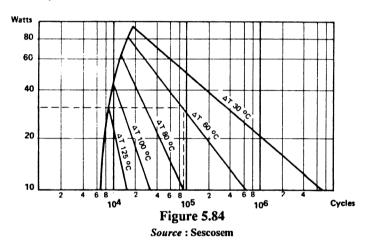

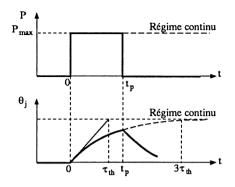

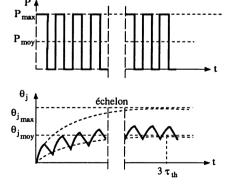

| 5.5.       | Problè   | mes thermiques en régime impulsionnel                        | 267        |

|            | 5.5.1.   | Problèmes thermiques en général                              | 267        |

|            | 550      | 5.5.1.1. Fatigue thermique des transistors de puissance      | 267<br>268 |

|            | 3.3.2.   | Régime impulsionnel                                          | 268        |

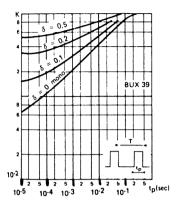

|            |          | 5.5.2.1. Impédance thermique                                 |            |

|            |          | 5.5.2.2. Série d'impulsions                                  | 269        |

|            | 553      | 5.5.2.3. Impulsion unique                                    | 270        |

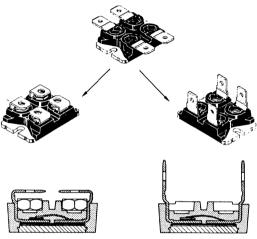

|            | 5.5.5.   | Boîtiers et radiateurs                                       | 271        |

|            | -        | . Intégration des fonctions analogiques                      | 279        |

| 6.1.       |          | tation succincte des circuits intégrés analogiques           | 279        |

|            | 6.1.1.   | Fonctions linéaires classiques                               | 279        |

|            |          | 6.1.1.1. Famille des amplificateurs opérationnels            | 279        |

|            |          | 6.1.1.2. Famille des régulateurs                             | 280        |

|            |          | 6.1.1.3. Famille des comparateurs de tensions                | 280        |

|            | 6.1.2.   | Commutateurs analogiques                                     | 281        |

|            | 6.1.3.   | Fonctions spéciales                                          | 281        |

| 6.2.       | Techn    | ologie des fonctions linéaires classiques                    | 282        |

|            |          | Technologie bipolaire                                        | 282        |

|            |          | 6.2.1.1. Composants de base                                  | 282        |

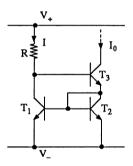

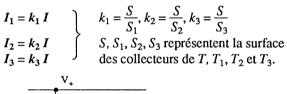

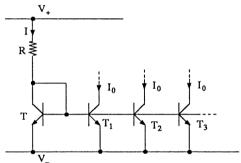

|            |          | 6.2.1.2. Fonctions de base                                   | 287        |

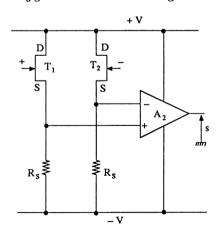

|            | 6.2.2.   | Technologie MOS                                              | 299        |

|            |          | 6.2.2.1. Composants de base                                  | 300        |

|            |          | 6.2.2.2. Fonctions de base                                   | 301        |

|            | 6.2.3.   | Technologie BIFET et BIMOS                                   | 314        |

|            |          | 6.2.3.1. Technologie BIFET                                   | 314        |

|            |          | 6.2.3.2. Technologie BIMOS                                   | 315        |

|            | 6.2.4    | Quelques exemples de fonctions linéaires                     | 315        |

|            | 0        | 6.2.4.1. Comparaison des technologies bipolaires et MOS      | 315        |

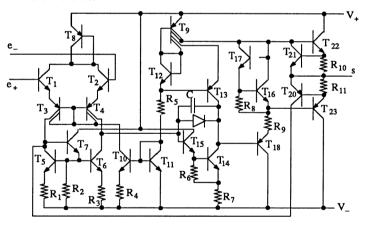

|            |          | 6.2.4.2. Amplificateur opérationnel bipolaire 741            | 316        |

|            |          | 6.2.4.3. Amplificateur opérationnel BIFET, LT1055            | 318        |

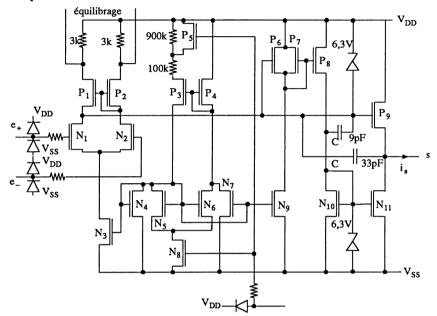

|            |          | 6.2.4.4. Amplificateur opérationnel CMOS, ICL7611            | 319        |

| <i>(</i> ) | <b>C</b> | -                                                            |            |

| 0.3.       |          | nutateurs analogiques                                        | 320<br>320 |

|            | 0.3.1.   | Généralités                                                  |            |

|            |          | 6.3.1.1. Composants utilisés                                 | 320<br>320 |

|            |          | 6 3 1 2 Liomaines d'application des commitateurs analogiques | - 3 Z U    |

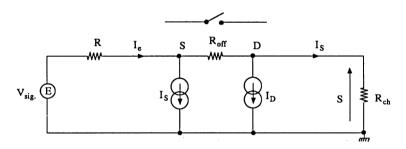

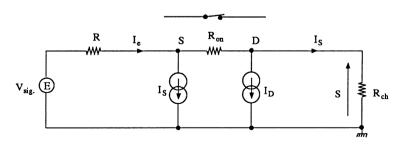

|      |         | 6.3.1.3. Schémas équivalents statiques d'un commutateur     |     |

|------|---------|-------------------------------------------------------------|-----|

|      |         | à transistors à effet de champ                              | 321 |

|      |         | 6.3.1.4. Schémas équivalents dynamiques d'un commutateur    |     |

|      |         | à transistor à effet de champ                               | 322 |

|      |         | 6.3.1.5. Caractéristiques utilisées                         | 322 |

|      | 6.3.2.  | Commutateurs à JFET                                         | 325 |

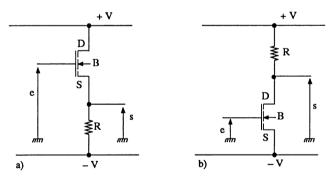

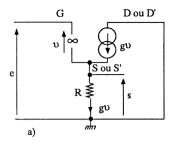

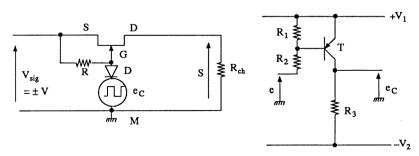

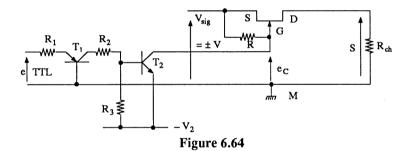

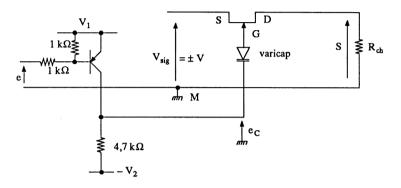

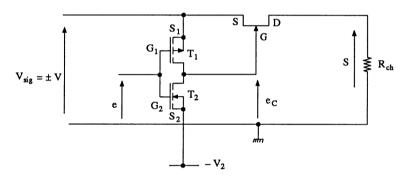

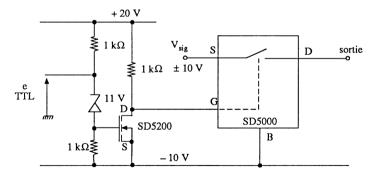

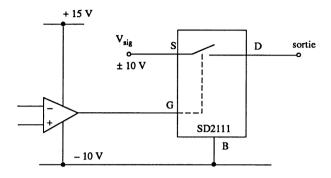

|      |         | 6.3.2.1. Principe de la commande                            | 325 |

|      |         | 6.3.2.2. Procédés de commande                               | 326 |

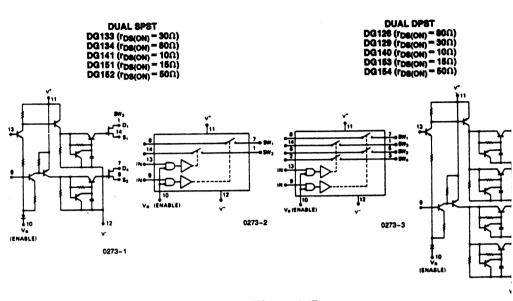

|      |         | 6.3.2.3. Exemples de circuits intégrés commercialisés       | 329 |

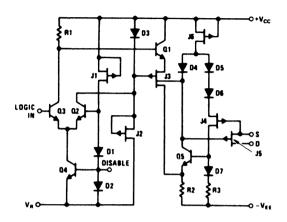

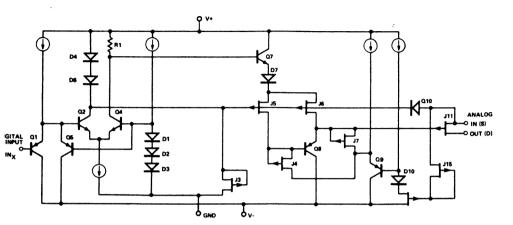

|      | 6.3.3.  | Commutateurs à MOSFET                                       | 333 |

|      |         | 6.3.3.1. Principe de la commande                            | 334 |

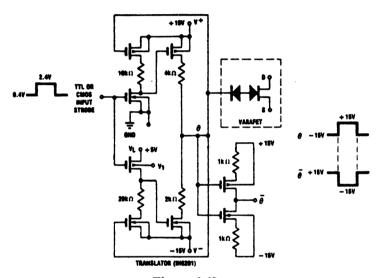

|      |         | 6.3.3.2. Exemples réels et procédés de commande             | 335 |

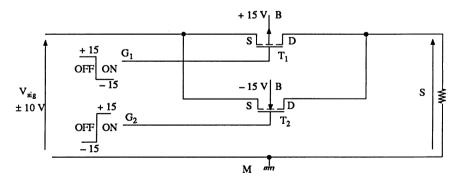

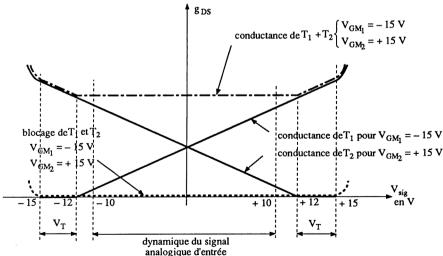

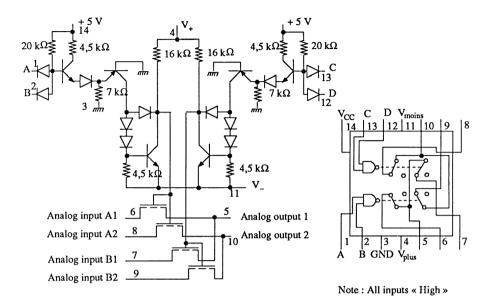

|      | 6.3.4.  | Commutateurs CMOS                                           | 337 |

|      |         | 6.3.4.1. Principe de la commande                            | 337 |

|      |         | 6.3.4.2. Exemples pratiques de commutateurs                 | 339 |

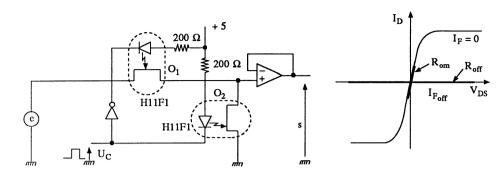

|      | 6.3.5.  | Optocommutateurs diode-JFET                                 | 345 |

|      |         | Comparaison des commutateurs                                | 346 |

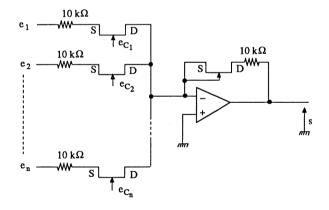

|      |         | Quelques exemples d'application des commutateurs            | 347 |

|      |         | 6.3.7.1. Commutateurs simples                               | 347 |

|      |         | 6.3.7.2. Multiplexeurs                                      | 348 |

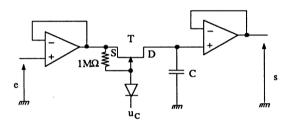

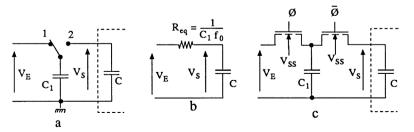

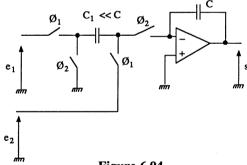

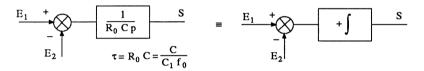

|      | 6.3.8.  | Technique et application des capacités commutées            | 350 |

|      |         | 6.3.8.1. Principe                                           | 350 |

|      |         | 6.3.8.2. Filtres à capacités commutées                      | 351 |

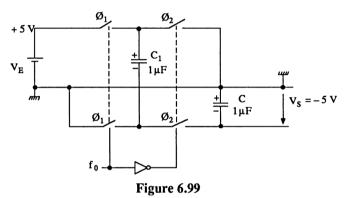

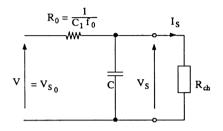

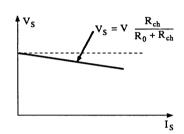

|      |         | 6.3.8.3. Alimentations à découpage                          | 355 |

|      |         | 6.3.8.4. Autres applications des capacités commutées        | 356 |

| 64   | Circui  | ts spéciaux                                                 | 356 |

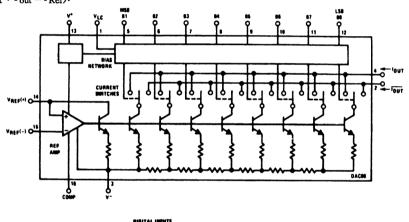

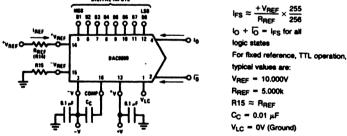

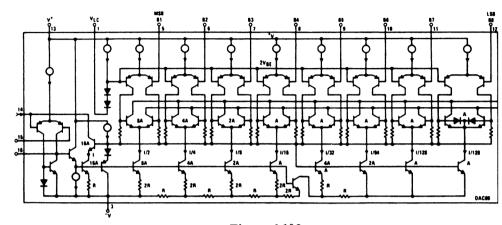

| 0.7. |         | Convertisseur numérique-analogique                          | 357 |

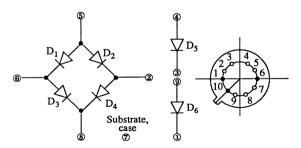

|      |         | Réseau de diodes                                            | 358 |

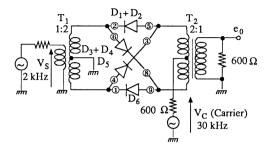

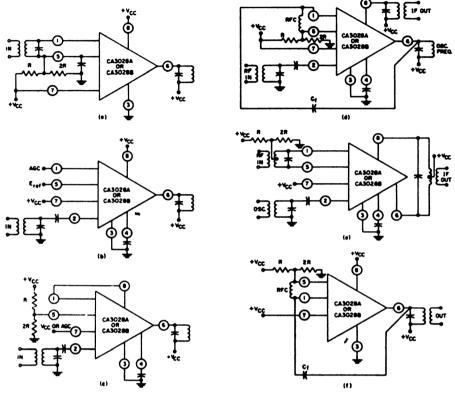

|      |         | Circuit intégré radiofréquences                             | 359 |

|      |         | Circuits intégrés en arséniure de gallium                   | 360 |

|      |         | Dispositifs à transfert de charge CCD                       | 361 |

|      |         |                                                             | 501 |

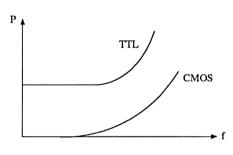

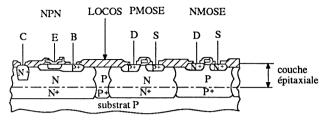

| Cha  | pitre 7 | . Intégration des fonctions logiques (ou numériques)        | 365 |

| 7.1. | Préser  | ntation succincte des circuits intégrés numériques          | 365 |

|      |         | Essai de classifications                                    | 365 |

|      |         | 7.1.1.1. Classification en fonction du nombre de composants | 365 |

|      |         | 7.1.1.2. Classification en fonction de la technologie       | 367 |

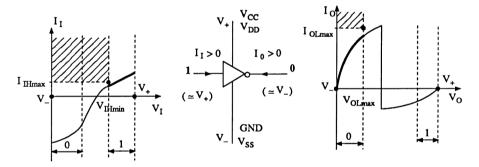

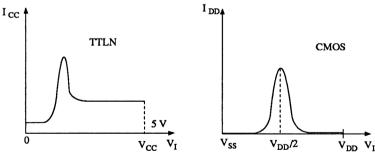

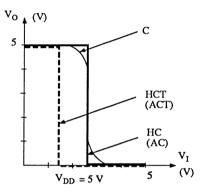

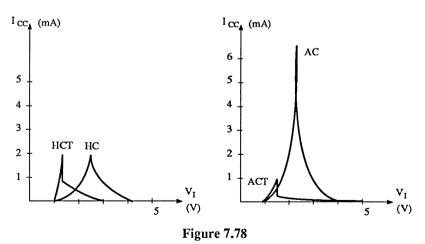

|      | 7.1.2.  | Caractéristiques statistiques                               | 369 |

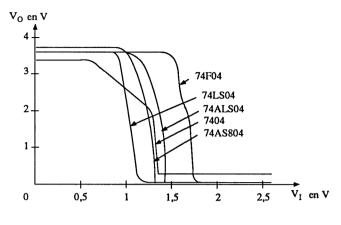

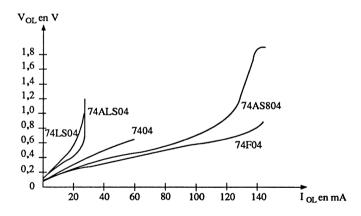

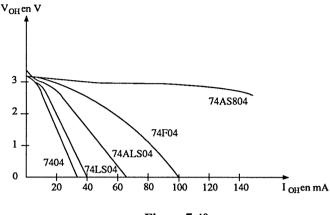

|      |         | 7.1.2.1. Caractéristiques d'entrée et de sortie             | 369 |

|      |         | 7.1.2.2. Caractéristiques d'alimentation                    | 373 |

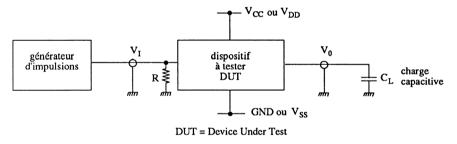

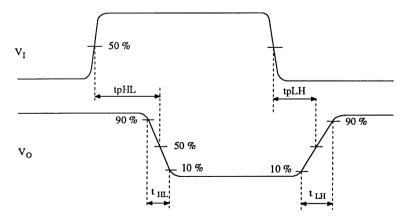

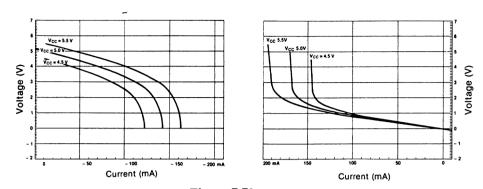

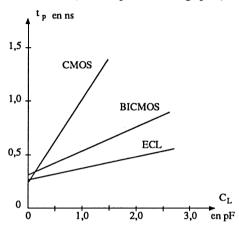

|      | 7.1.3.  | Caractéristiques dynamiques                                 | 374 |

|      |         | 7.1.3.1. Temps de réponse                                   | 374 |

|      |         | 7.1.3.2. Facteur de mérite                                  | 375 |

|      |         |                                                             |     |

| 7.2. | Circui | its bipola | ires saturés                                           | 375 |

|------|--------|------------|--------------------------------------------------------|-----|

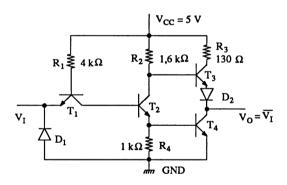

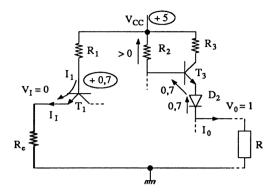

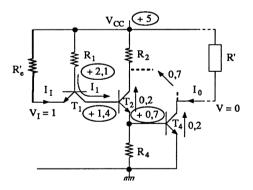

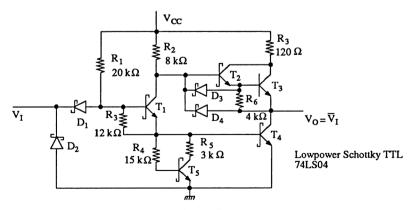

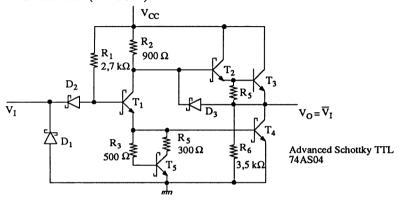

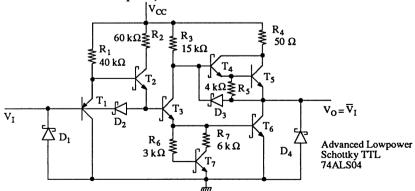

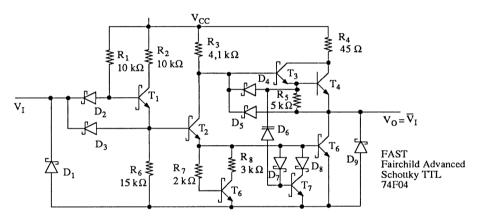

|      | 7.2.1. | Famille    | TTL                                                    | 375 |

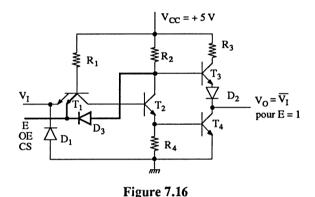

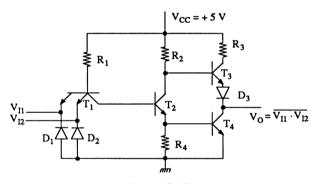

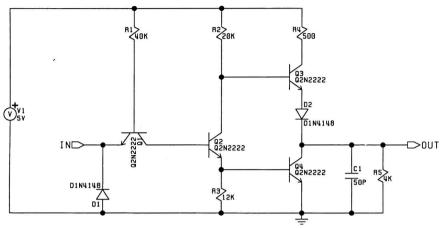

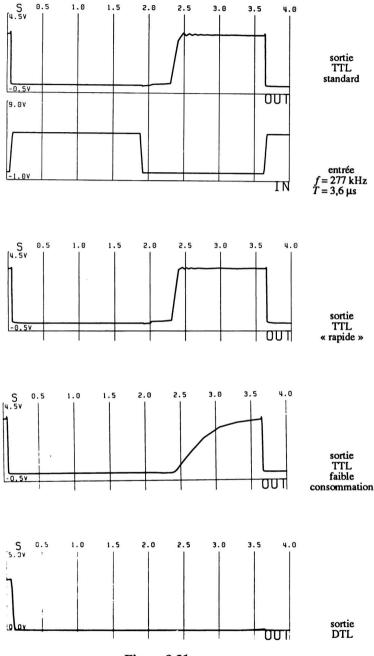

|      |        | 7.2.1.1.   | Principe de l'inverseur TTL standard 7404              | 376 |

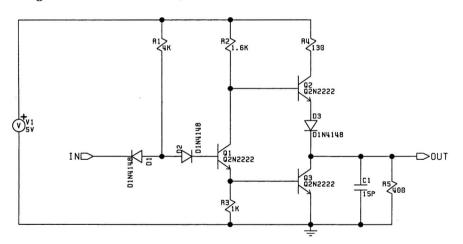

|      |        | 7.2.1.2.   | Différents types d'inverseurs TTL                      | 378 |

|      |        | 7.2.1.3.   | Autres opérateurs TTL                                  | 381 |

|      |        | 7.2.1.4.   | Caractéristiques et performances des circuits TTL      | 385 |

|      | 7.2.2. | Famille    | I <sup>2</sup> L                                       | 387 |

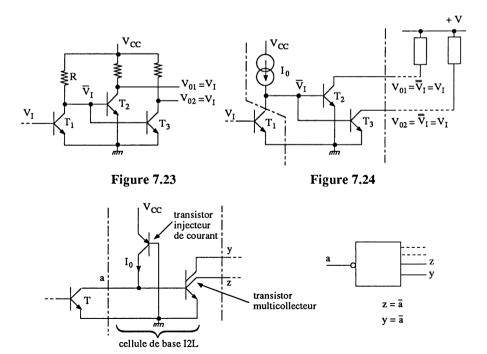

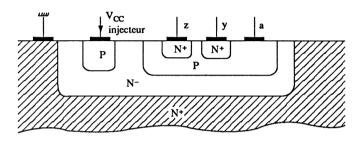

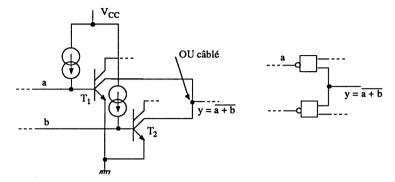

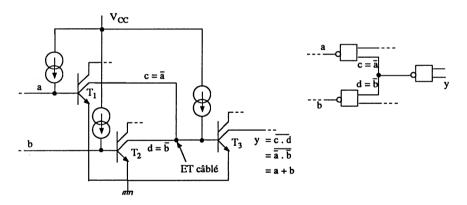

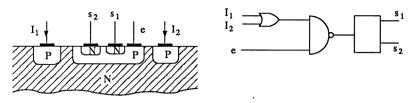

|      |        |            | Principe et caractéristiques de l'I <sup>2</sup> L     | 387 |

|      |        |            | Réalisation des fonctions numériques                   | 388 |

| 7.3. | Circui |            | ires non saturés                                       | 390 |

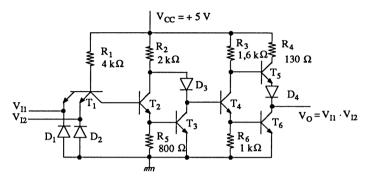

|      |        |            | TTL Schottky                                           | 390 |

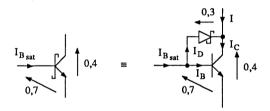

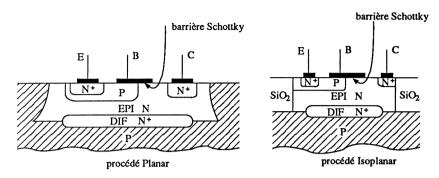

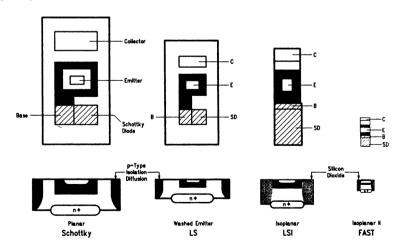

|      |        |            | Présentation de la technologie TTL Schottky            | 390 |

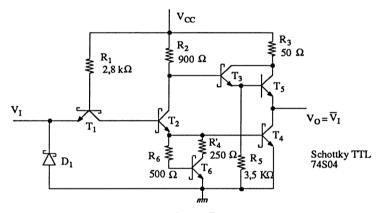

|      |        |            | Inverseurs TTL Schottky                                | 393 |

|      |        |            | Caractéristiques et performances des circuits TTL      |     |

|      |        |            | Schottky                                               | 395 |

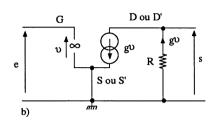

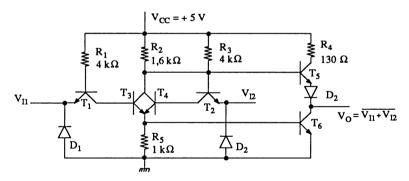

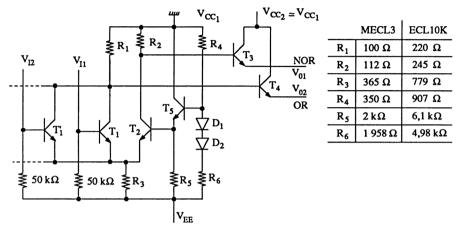

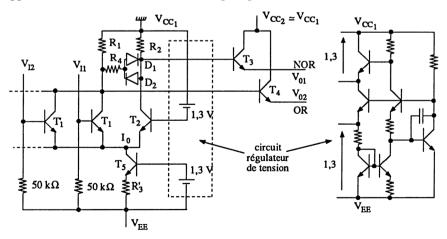

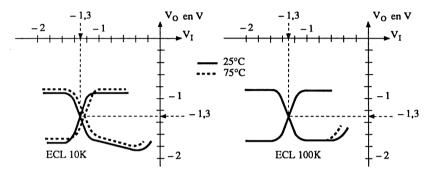

|      | 7.3.2. | Famille    | ECL                                                    | 399 |

|      |        |            | Présentation de la technologie ECL                     | 399 |

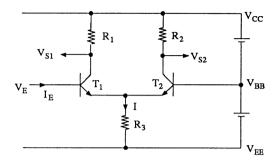

|      |        |            | Élément de base de la technologie ECL                  | 399 |

|      |        |            |                                                        |     |

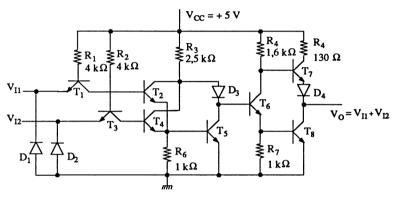

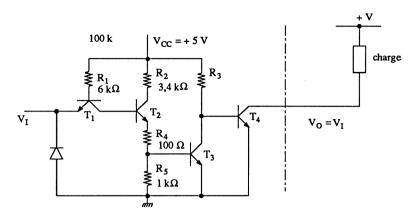

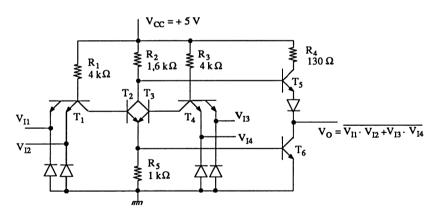

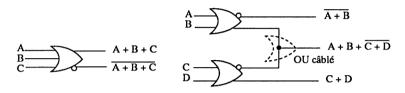

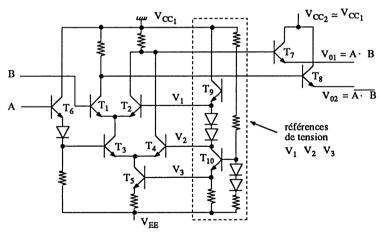

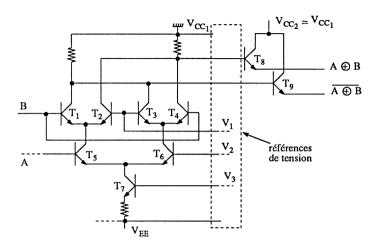

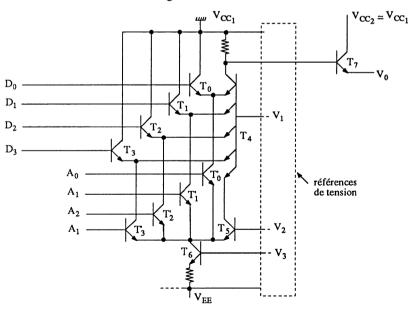

|      |        |            | Évolution de l'opérateur OU-OU                         | 401 |

|      |        |            | Principe de l'assemblage d'opérateurs ECL              | 404 |

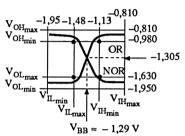

|      |        |            | Caractéristiques et performances de la technologie ECL |     |

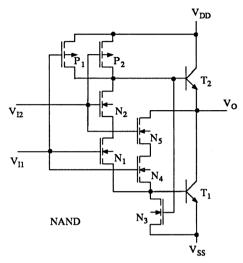

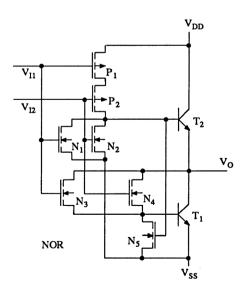

| 7.4. |        | ts MOS     |                                                        | 408 |

|      | 7.4.1. |            | NMOS                                                   | 408 |

|      |        |            | Présentation de la technologie NMOS                    | 408 |

|      |        |            | Inverseurs NMOS                                        | 409 |

|      |        |            | Autres opérateurs NMOS                                 | 412 |

|      |        | 7.4.1.4.   | Caractéristiques et performances de la technologie     |     |

|      |        |            | NMOS                                                   | 414 |

|      | 7.4.2. |            | CMOS                                                   | 416 |

|      |        |            | Présentation de la technologie CMOS                    | 416 |

|      |        | 7.4.2.2.   | Inverseurs CMOS                                        | 418 |

|      |        | 7.4.2.3.   | Autres opérateurs CMOS                                 | 420 |

|      |        | 7.4.2.4.   | Caractéristiques et performances de la technologie     |     |

|      |        |            | CMOS                                                   | 422 |

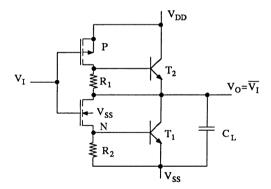

| 7.5. |        |            | OS                                                     | 428 |

|      |        |            | tion de la technologie BICMOS                          | 428 |

|      |        |            | urs BICMOS                                             | 429 |

|      |        |            | istiques de la technologie BICMOS                      | 431 |

| 7.6. |        |            |                                                        | 431 |

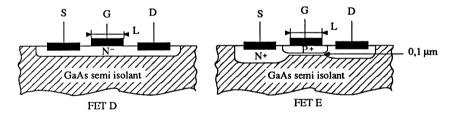

|      |        |            | tion de la technologie GaAs                            | 431 |

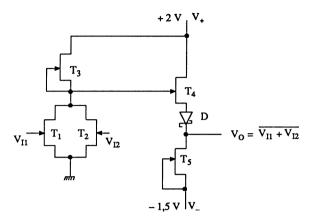

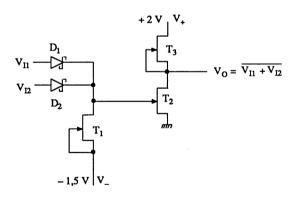

|      | 7.6.2. |            | ırs GaAs                                               | 432 |

|      |        |            | Opérateurs à FETD                                      | 432 |

|      |        | 7622       | Opérateurs à FETE                                      | 434 |

|      |         | Caractéristiques et performances de la technologie GaAs | 435 |

|------|---------|---------------------------------------------------------|-----|

| 7.7. | Circui  | ts d'interface                                          | 436 |

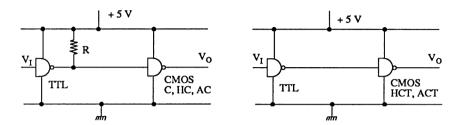

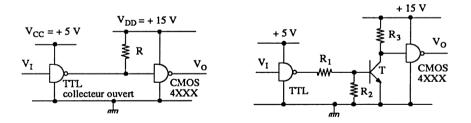

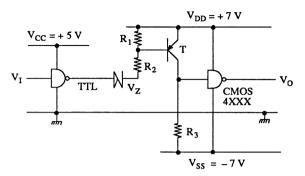

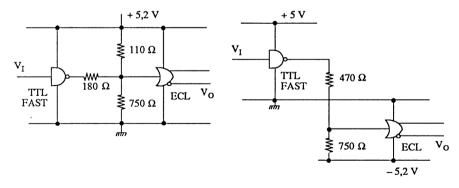

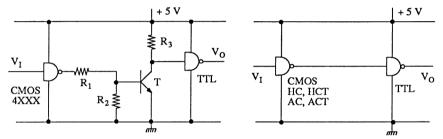

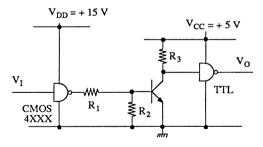

|      | 7.7.1.  | Interfaces TTL vers d'autres technologies               | 436 |

|      |         | 7.7.1.1. Interfaces TTL → CMOS                          | 436 |

|      |         | 7.7.1.2. Interfaces TTL $\rightarrow$ ECL               | 438 |

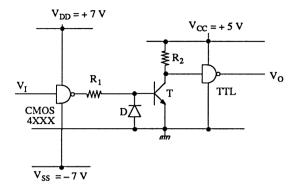

|      | 7.7.2.  | Interfaces CMOS vers d'autres technologies              | 439 |

|      |         | 7.7.2.1. Interfaces CMOS → TTL                          | 439 |

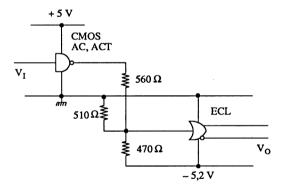

|      |         | 7.7.2.2. Interface CMOS $\rightarrow$ ECL               | 44( |

|      | 7.7.3.  | Interfaces ECL vers d'autres technologies               | 44( |

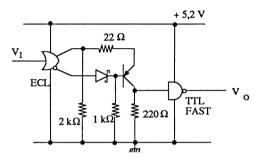

|      |         | 7.7.3.1. Interfaces ECL $\rightarrow$ TTL               | 441 |

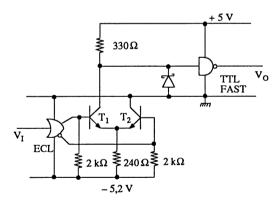

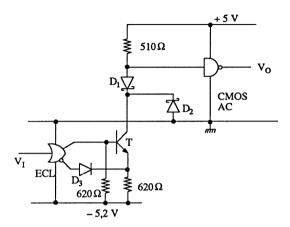

|      |         | 7.7.3.2. Interface ECL $\rightarrow$ CMOS               | 441 |

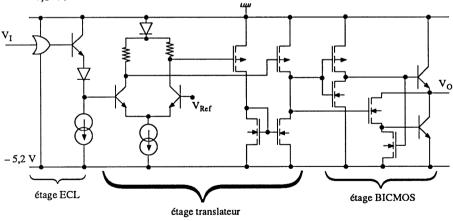

|      |         | 7.7.3.3. Interface ECL $\rightarrow$ BICMOS             | 442 |

| Cha  | m:4ma 0 | . Circuits intégrés spécifiques – ASIC                  | 443 |

| CHa  | pure o  | station agricult day ASIC                               | 443 |

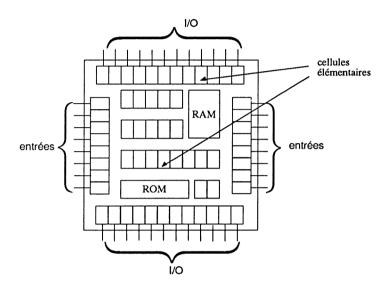

| 8.1. | Presen  | ntation générale des ASIC                               | 443 |

|      |         | Qu'est-ce qu'un ASIC ?                                  |     |

|      | 8.1.2.  | Le monde des ASIC                                       | 444 |

|      |         | 8.1.2.1. ASIC programmables sur site                    | 444 |

|      |         | 8.1.2.2. ASIC programmables chez les « fondeurs »       | 446 |

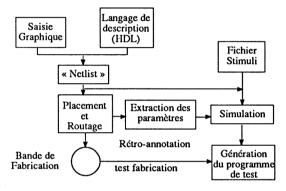

|      | 0.4.0   | 8.1.2.3. Procédure de conception des ASIC               | 448 |

|      | 8.1.3.  | Avantages et inconvénients des ASIC                     | 449 |

|      |         | 8.1.3.1. Avantages                                      | 449 |

|      |         | 8.1.3.2. Inconvénients                                  | 449 |

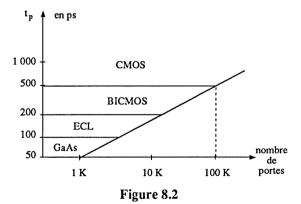

|      |         | Quelques chiffres                                       | 450 |

| 8.2. |         | ologie des ASIC                                         | 452 |

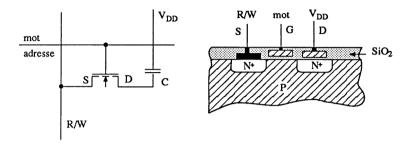

|      | 8.2.1.  | Rappels concernant les mémoires électriques             | 452 |

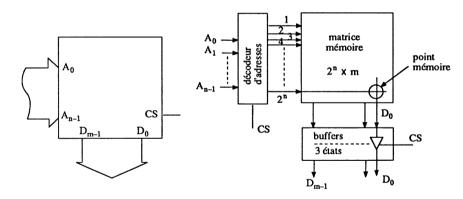

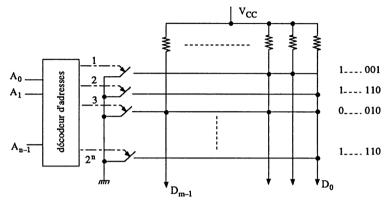

|      |         | 8.2.1.1. Mémoires mortes ROM                            | 452 |

|      |         | 8.2.1.2. Mémoires vives RAM                             | 454 |

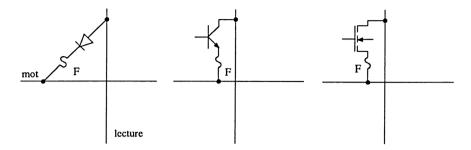

|      |         | 8.2.1.3. Mémoires mortes PROM                           | 450 |

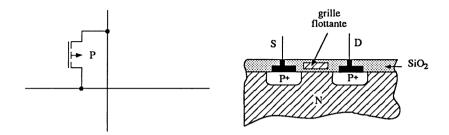

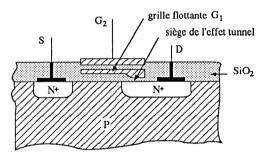

|      |         | 8.2.1.4. Mémoires mortes EPROM                          | 45  |

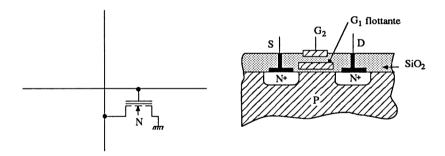

|      |         | 8.2.1.5. Mémoires mortes EEPROM                         | 459 |

|      | 8.2.2.  | ASIC programmables sur site                             | 459 |

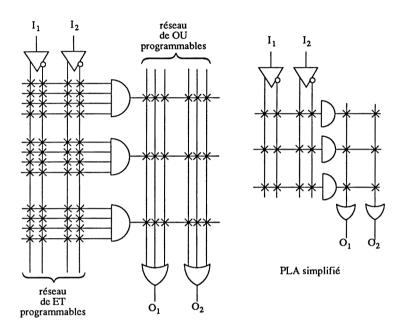

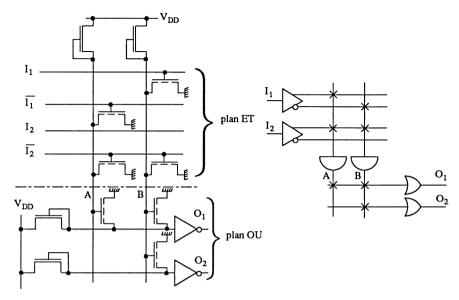

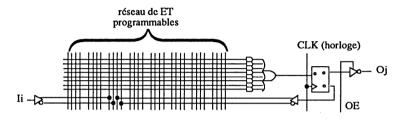

|      |         | 8.2.2.1. PLA ou FPLA                                    | 459 |

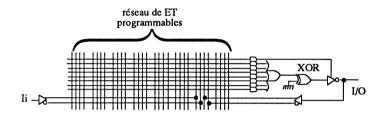

|      |         | 8.2.2.2. PLD, EPLD ou EEPLD combinatoires               | 46  |

|      |         | 8.2.2.3. PLD, EPLD ou EEPLD séquentiels                 | 462 |

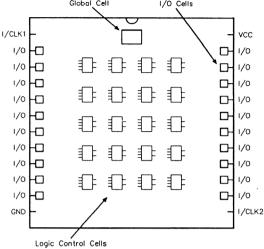

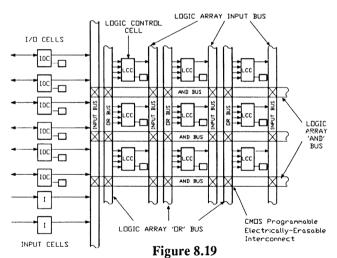

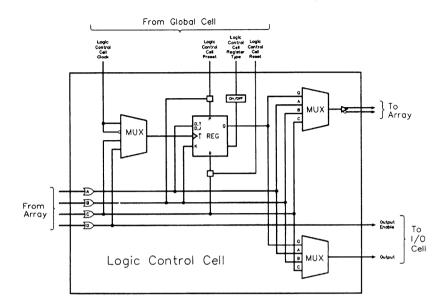

|      |         | 8.2.2.4. Matrices programmables                         | 463 |

|      |         | 8.2.2.5. Réseaux prédiffusés programmables              | 46  |

|      | 8.2.3.  | ASIC programmables chez le « fondeur »                  | 468 |

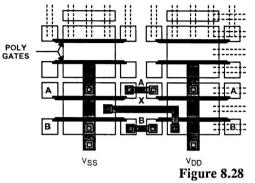

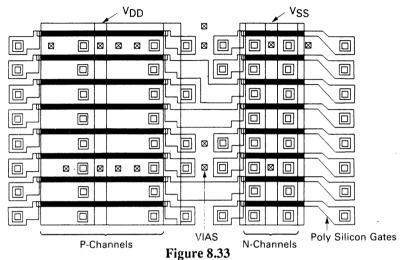

|      |         | 8.2.3.1. Réseaux prédiffusés                            | 468 |

|      |         | 8.2.3.2. Réseaux précaractérisés                        | 472 |

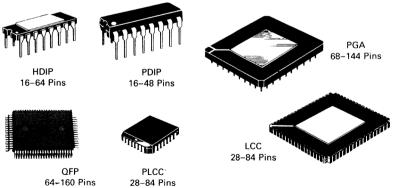

|      |         | Boîtiers pour ASIC                                      | 473 |

| 8.3. |         | ples d'ASIC                                             | 474 |

|      | 8.3.1.  | Réseau prédiffusé numérique                             | 474 |

|      | 8.3.2.  | Réseau prédiffusé analogique                            | 479 |

| 8.4. | Mini g  | glossaire des ASIC                                                                           | 485 |

|------|---------|----------------------------------------------------------------------------------------------|-----|

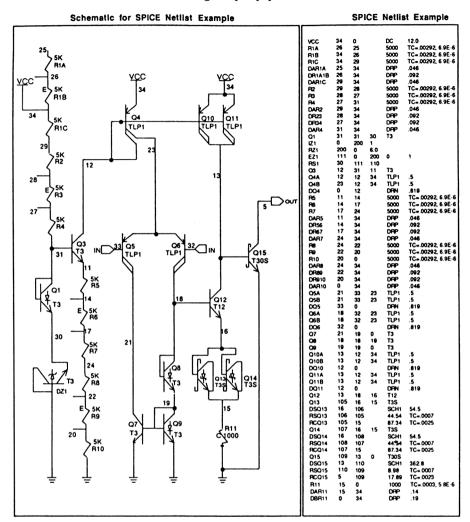

| Cha  | pitre 9 | . Simulation analogique                                                                      | 489 |

| 9.1. | Modè    | e SPICE                                                                                      | 489 |

|      | 9.1.1.  | Introduction                                                                                 | 489 |

|      | 9.1.2.  | Diodes                                                                                       | 490 |

|      |         | 9.1.2.1. Désignation en Net List                                                             | 490 |

|      |         | 9.1.2.2. Paramètres SPICE                                                                    | 490 |

|      |         | 9.1.2.3. Exemples de paramètres utilisés en simulation                                       | 492 |

|      | 9.1.3.  | Transistors bipolaires (BJT, NPN et PNP)                                                     | 492 |

|      |         | 9.1.3.1. Désignation en Net List                                                             | 492 |

|      |         | 9.1.3.2. Paramètres SPICE                                                                    | 492 |

|      |         | 9.1.3.3. Exemples de paramètres utilisés en simulation                                       | 494 |

|      | 9.1.4.  | Transistors JFET (N et P)                                                                    | 494 |

|      |         | 9.1.4.1. Désignation en Net List                                                             | 494 |

|      |         | 9.1.4.2. Paramètres SPICE                                                                    | 494 |

|      |         | 9.1.4.3. Exemple de paramètres utilisés en simulation                                        | 495 |

|      | 9.1.5.  | Transistors MOSFET                                                                           | 495 |

|      |         | 9.1.5.1. Désignation en Net List                                                             | 495 |

|      |         | 9.1.5.2. Paramètres SPICE                                                                    | 496 |

|      |         | 9.1.5.3. Exemples de paramètres utilisés en simulation                                       | 497 |

| 9.2. | Exem    | ples simples de simulation analogique                                                        | 497 |

|      |         | Méthodologie                                                                                 | 497 |

|      | 9.2.2.  | Effet de la température sur une jonction-application à un                                    |     |

|      |         | thermomètre                                                                                  | 498 |

|      | 9.2.3.  | Caractéristiques $I_{\mathbb{C}}(V_{\mathbb{C}\mathbb{E}})$ pour un transistor bipolaire NPN | 500 |

|      |         | Influence de la température sur une polarisation                                             | 502 |

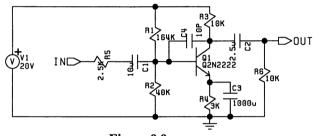

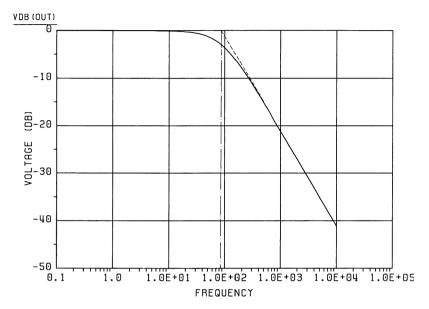

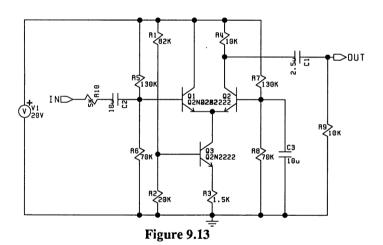

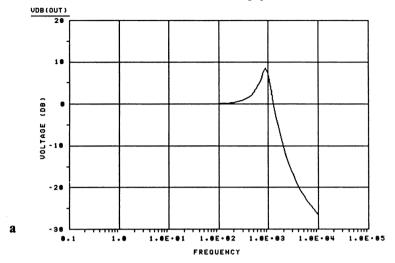

|      |         | Réponse en fréquence des montages fondamentaux                                               | 503 |

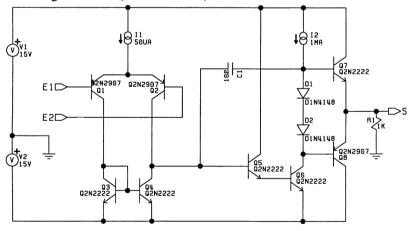

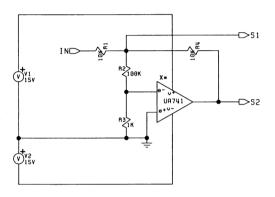

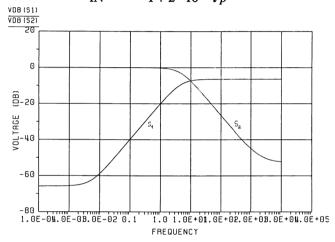

|      |         | Amplificateur opérationnel en technologie bipolaire                                          | 509 |

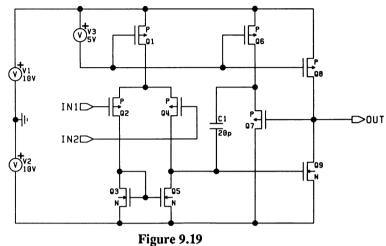

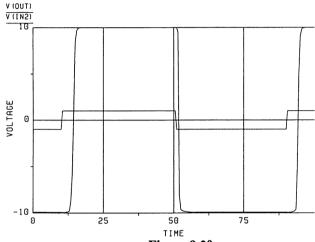

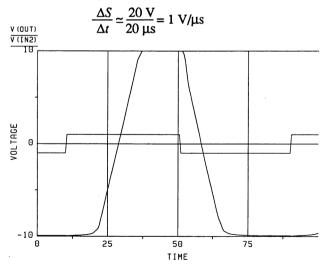

|      |         | Amplificateur opérationnel en technologie CMOS                                               | 514 |

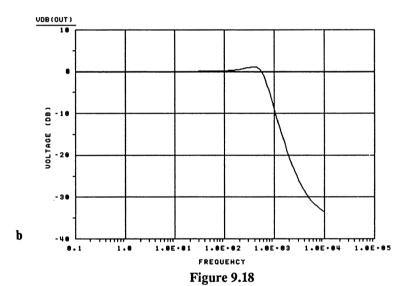

|      |         | Réponse en fréquence en boucle ouverte d'un amplificateur                                    |     |

|      |         | opérationnel                                                                                 | 518 |

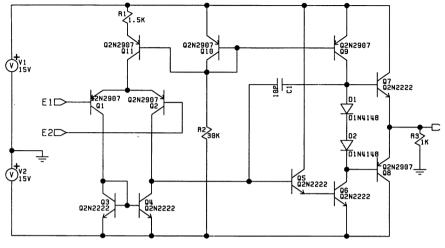

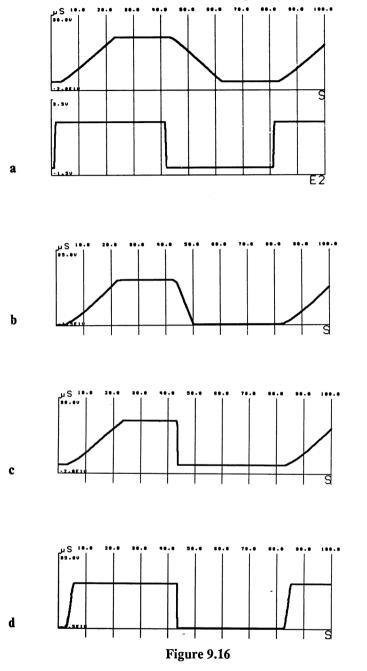

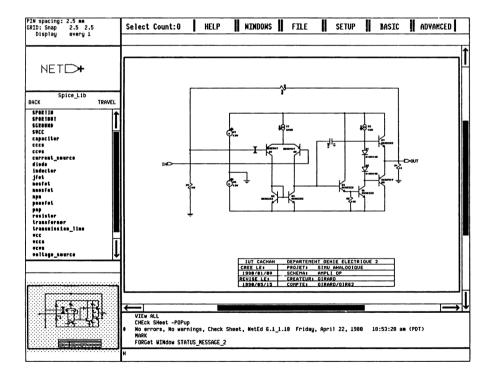

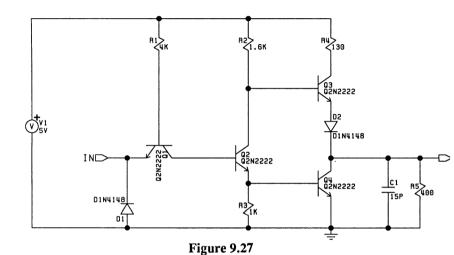

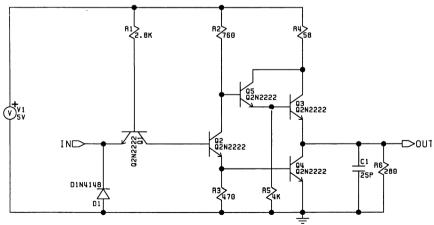

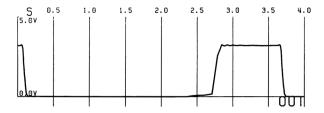

|      | 9.2.9.  | Opérateurs TTL à éléments discrets                                                           | 519 |

| Ribl | liogran | hie                                                                                          | 525 |

#### **CHAPITRE 4**

### Transistors à effet de champ

#### 4.1. PRÉSENTATION, PRINCIPE, THÉORIE DES TRANSISTORS A EFFET DE CHAMP

Le principe des transistors à effet de champ (TEC ou FET – field effect transistor) a été imaginé dans les années trente par J.E. Lilienfeld. Toutefois, la difficulté de contrôle de la conduction n'a permis leur réalité physique qu'à partir de 1952 (grâce à Shockley) et leur intégration en 1962 par la société Fairchild introduisant le procédé silicium planar (procédé impossible à utiliser avec le germanium).

Les transistors à effet de champ n'ont cessé d'évoluer, et leurs performances actuelles dépassent, dans beaucoup de domaines, celles des transistors bipolaires (micro-ondes, commutation rapide de puissance, certains circuits intégrés analogiques et numériques...).

## 4.1.1. IDÉE DIRECTRICE, PRINCIPES SIMPLIFIÉS, DOMAINES D'APPLICATION

#### 4.1.1.1. Conduction dans un barreau semiconducteur

Le principe des transistors à effet de champ consiste à utiliser un barreau de matériau semiconducteur dopé N ou P et à faire varier sa conductibilité en lui appliquant un champ électrique transversal (action électrostatique), par l'intermédiaire d'une électrode appelée grille, les autres électrodes (le drain et la source) étant les extrémités du barreau.

Si les dimensions de ce barreau dopé N sont : l, la largeur, d, l'épaisseur et L, la longueur, on détermine la conductance statique par la relation vue au paragraphe 1.3.3.5.

$$G = \frac{1}{R} = \frac{I}{V} = q N_{\rm D} \mu_{\rm e} \frac{ld}{L} = \sigma \frac{S}{L} = \frac{1}{\rho} \frac{S}{L}$$

avec I, courant circulant dans le barreau,

V, différence de potentiel,

q, charge de l'électron,

$N_{\rm D}$ , nombre d'atomes d'impuretés donatrices,

$\mu_{\rm e}$ , mobilité des électrons.

Une relation identique est obtenue avec un dopage de type P.

Ainsi, faire varier la conductance d'un barreau semiconducteur dopé, revient à modifier :

- soit sa section « fictive » (étranglement plus ou moins marqué de la zone active) ; c'est le cas des transistors à jonction JFET,

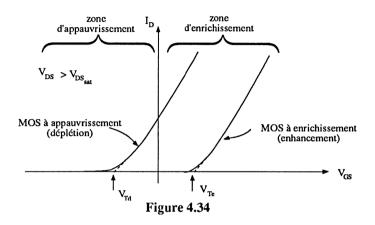

- soit sa densité en porteurs de charges (appauvrissement depletion ou enrichissement enhancement de la zone active). C'est le cas des transistors à grille isolée MOSFET.

Le transistor à effet de champ est aussi appelé transistor unipolaire car il ne met en œuvre qu'un seul type de porteurs.

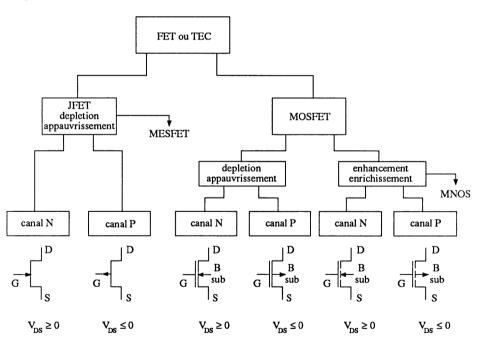

#### 4.1.1.2. Classification des transistors à effet de champ

En fonction des principes utilisés, nous pouvons adopter la classification suivante :

- Transistors à jonction PN (JFET). Le canal en silicium dopé N ou P est appauvri en polarisant la jonction canal-grille en inverse, ce qui a pour effet de faire varier l'épaisseur de la zone de déplétion de cette jonction, donc de diminuer la section du canal. Ces transistors ne peuvent être qu'à déplétion (appauvrissement).

- Transistors à barrière Schottky (MESFET MEtal Semiconductor FET). Ils fonctionnent suivant le même principe que les JFET (transistors à déplétion), toutefois, ils sont plus rapides à cause de l'utilisation des composés III-V (arséniure de gallium) et de l'absence des charges stockées dans la jonction, en commutation. Une variante est le TEGFET, présenté dans la section 4.5.

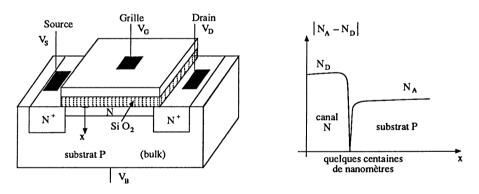

- Transistors à grille isolée (MOSFET Metal Oxide Semiconductor FET ou IGFET Insulated Gate FET). Ces transistors utilisent le phénomène d'accumulation de charges sur les armatures d'un condensateur plan dont l'une d'elles est le matériau semiconducteur dopé. La polarité de la tension appliquée sur la grille de commande permet d'appauvrir (déplétion) ou d'enrichir (enhancement) le canal.

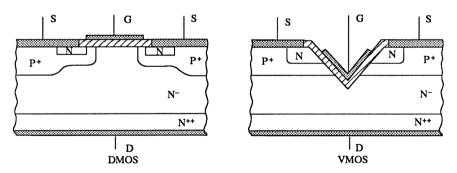

En plus de ces transistors classiques, on trouve certaines structures particulières telles que :

— les transistors MOS à double grille permettant la superposition de deux commandes. Le canal dopé peut être soit appauvri, soit enrichi ;

- les transistors à effet de champ de puissance qui sont des MOS à enrichissement et dont la dénomination commerciale diffère d'un fabricant à un autre (VMOS, HEXFET ...);

- les transistors à effet de champ, à grille isolée pour cellules mémoires (technologie intégrée) utilisant la superposition de deux isolants, l'un à base de nitrure de silicium, l'autre à base d'oxyde de silicium (d'où leur dénomination MNOS), permettant la conservation d'un état de charge (mémorisation) entre les deux zones isolantes.

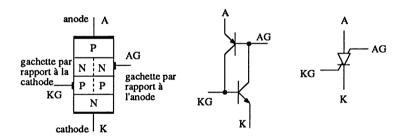

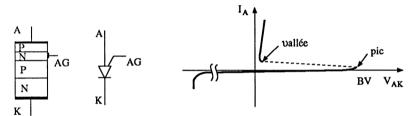

#### 4.1.1.3. Symbolisation

La symbolisation des composants est relativement liée à leur processus de fonctionnement. Les transistors à effet de champ ne font pas exception à la règle. Après en avoir énuméré les différents types, nous dressons l'organigramme de la figure 4.1.

Figure 4.1

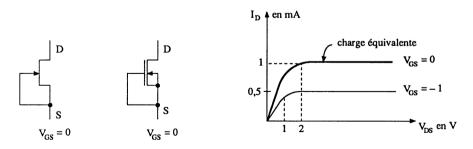

Un transistor à déplétion ou à appauvrissement possède un canal « riche » en porteurs de charges. Il est conducteur sans commande, alors le canal est représenté en trait continu.

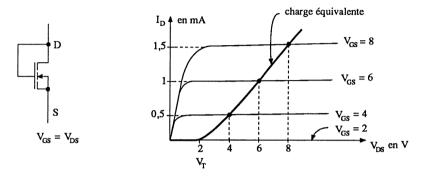

Un transistor à enhancement ou à enrichissement possède un canal dépourvu de charges actives (par exemple d'électrons pour un canal N). Il est non conducteur sans commande, alors le canal est représenté en trait discontinu.

La différenciation canal N ou canal P se fait par une flèche:

- flèche de jonction grille-canal pour le JFET,

- flèche canal-substrat pour le MOSFET (rappelons que le substrat ou bulk est le support semiconducteur dopé N ou P).

#### Remarques

- Les transistors à effet de champ sont référencés par rapport à la source :

- Commande entre grille et source par une tension  $V_{\rm GS}$  positive ou négative suivant le principe de fonctionnement.

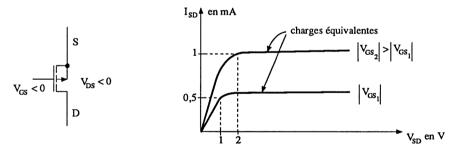

- Circuit de « puissance » entre drain et source avec une tension  $V_{\rm DS} \ge 0$  pour un canal N (déplacement d'électrons) ou une tension  $V_{\rm DS} \le 0$  pour un canal P (déplacement de « trous »).

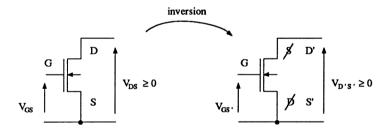

- De par leurs principes, les transistors à effet de champ sont symétriques, donc bidirectionnels. Inverser les électrodes de drain et de source impose d'inverser la polarité  $V_{\rm DS}$  et de changer la référence de la commande (figure 4.2). Toutefois, cette opération doit s'effectuer avec une extrême prudence, à cause, éventuellement :

- · de la dissymétrie de fabrication,

- des protections de commande entre grille et source,

- de la connexion substrat-source pour un MOSFET.

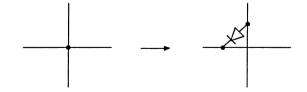

Figure 4.2

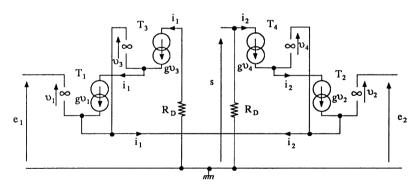

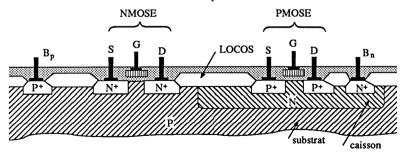

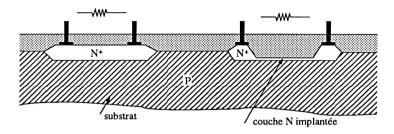

- En technologie intégrée, on rencontre différentes familles.

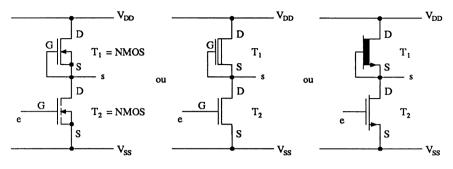

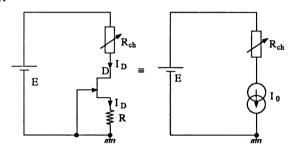

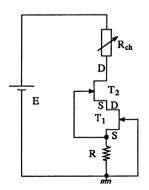

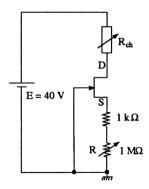

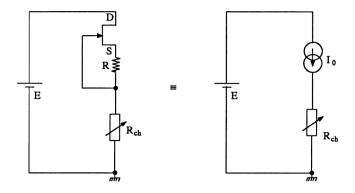

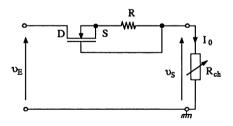

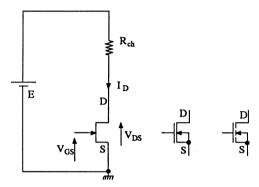

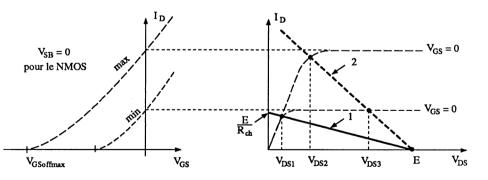

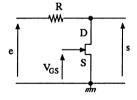

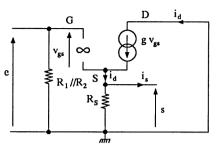

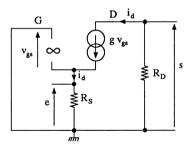

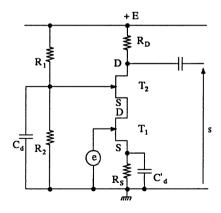

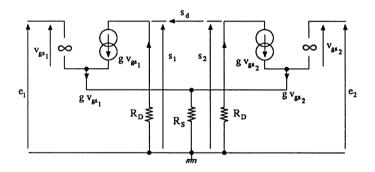

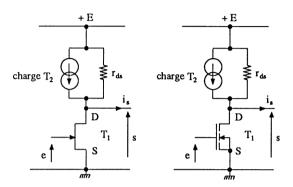

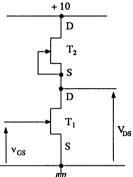

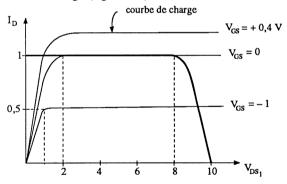

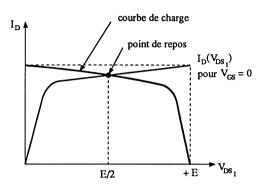

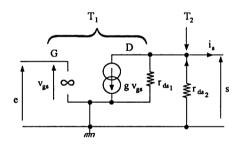

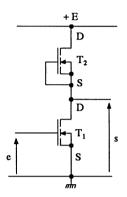

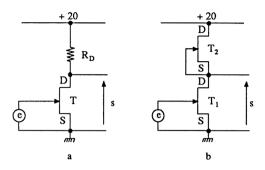

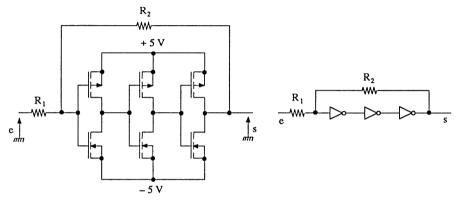

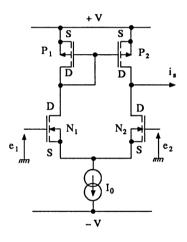

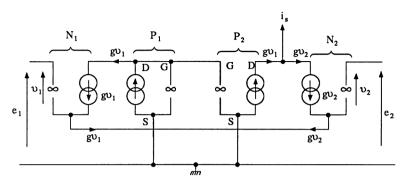

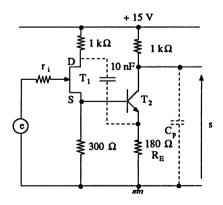

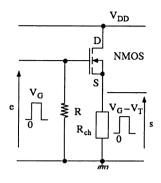

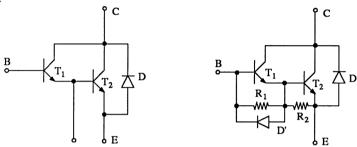

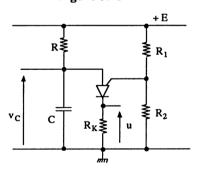

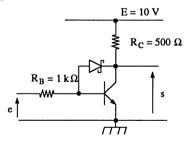

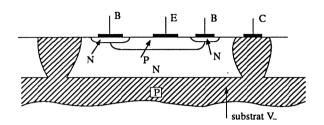

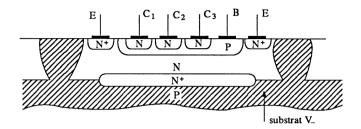

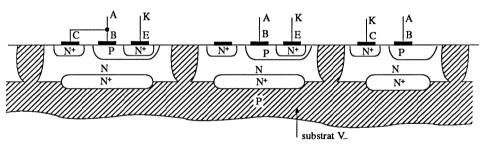

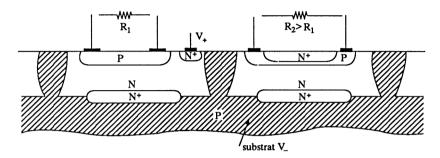

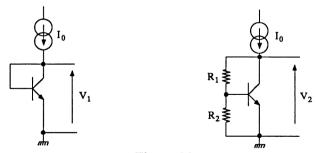

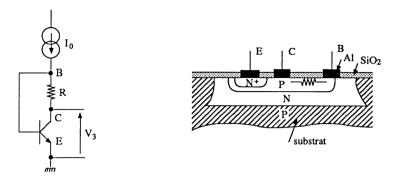

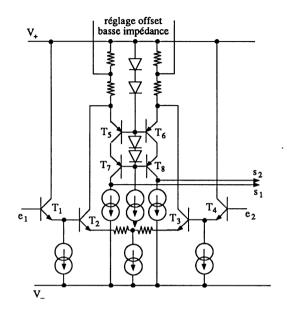

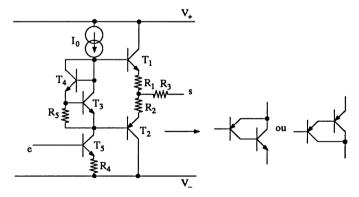

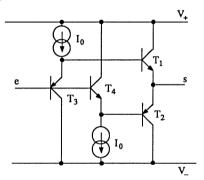

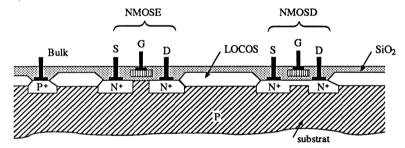

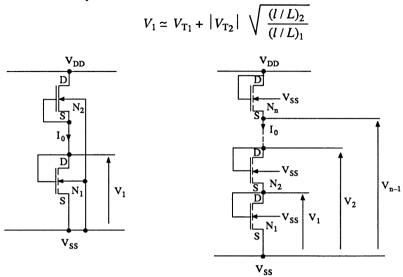

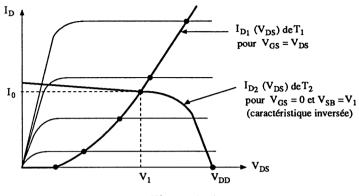

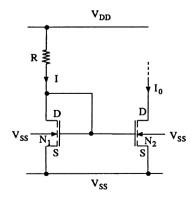

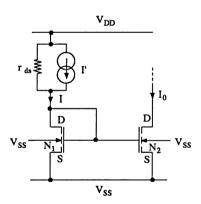

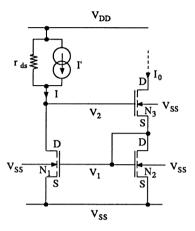

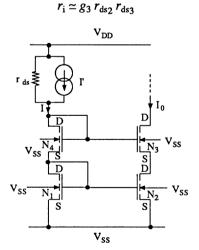

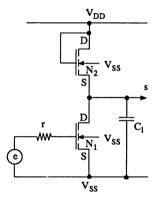

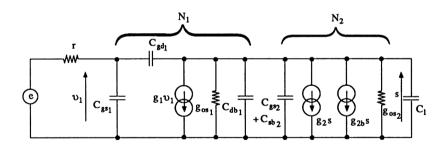

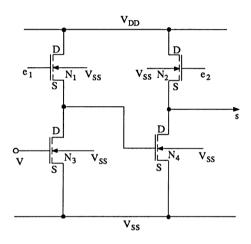

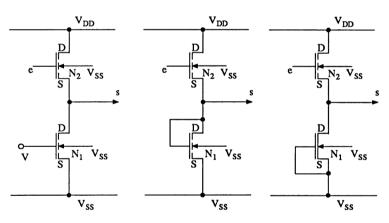

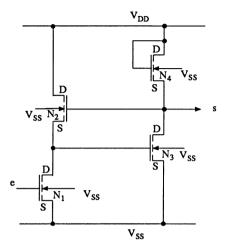

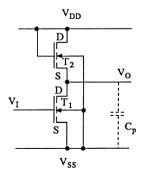

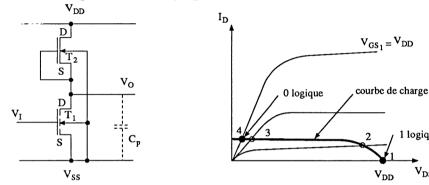

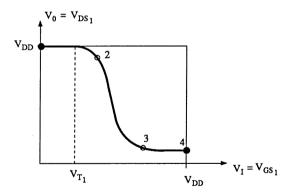

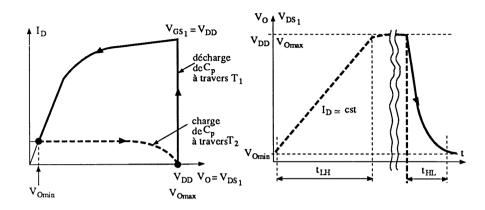

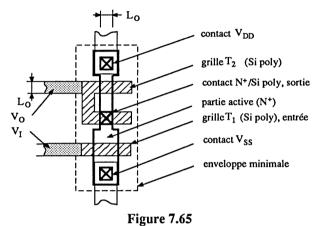

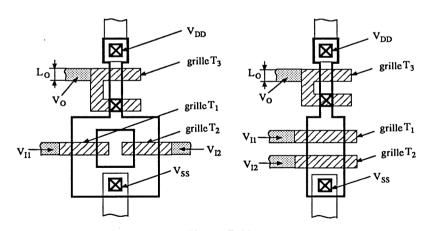

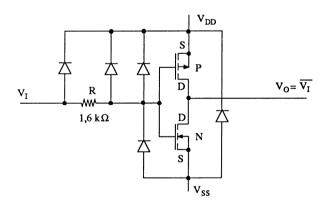

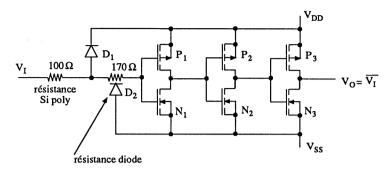

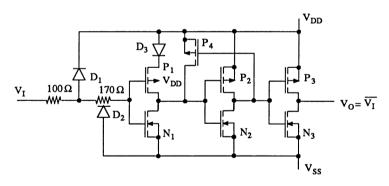

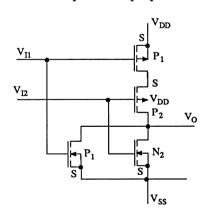

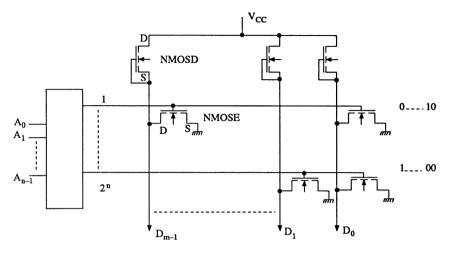

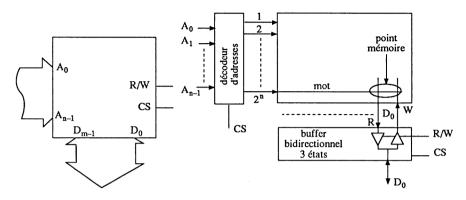

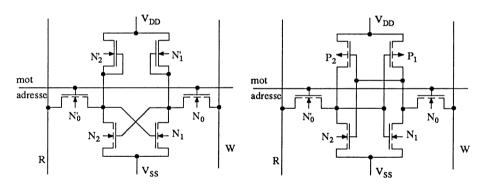

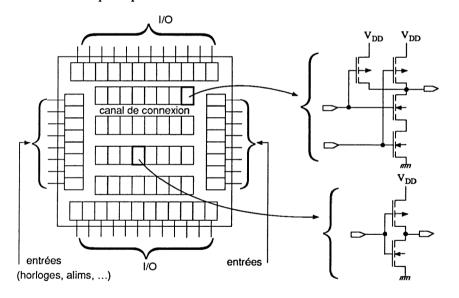

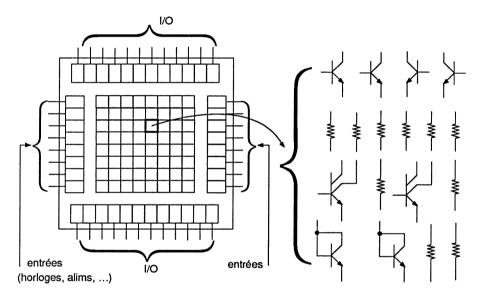

- Famille NMOS où tous les transistors sont à canal N (transistors uniquement à enrichissement ou association de transistors à enrichissement et à déplétion-EDMOS). La figure 4.3 représente un inverseur NMOS dont l'élément actif  $T_2$  est un transistor à enrichissement et la charge  $T_1$ , un transistor à appauvrissement (déplétion). Les schémas de droite utilisent une autre symbolisation souvent rencontrée. Dans certains cas, la charge  $T_1$  peut correspondre, elle aussi, à un transistor à enrichissement (voir chapitres 6 et 7).

Figure 4.3

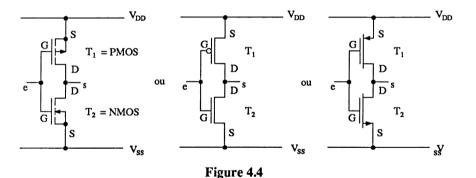

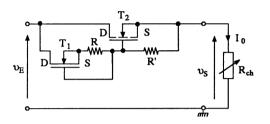

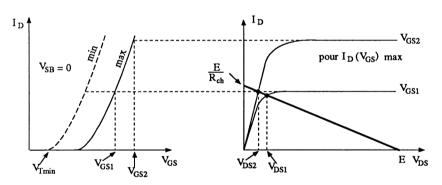

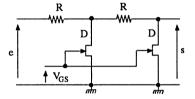

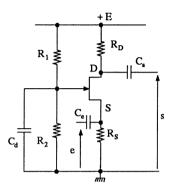

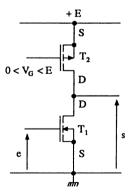

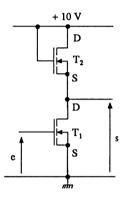

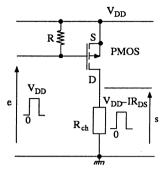

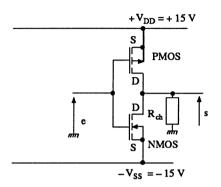

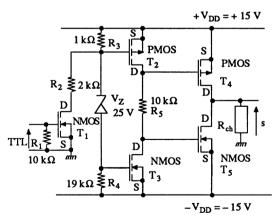

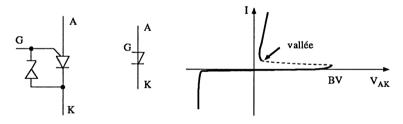

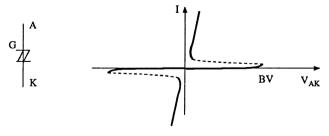

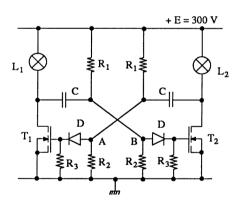

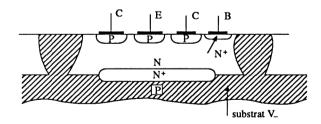

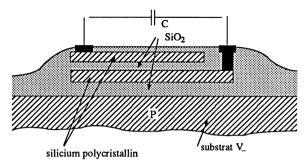

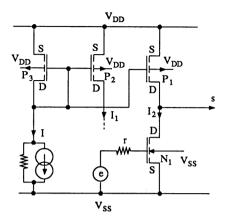

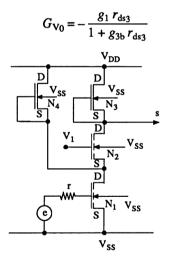

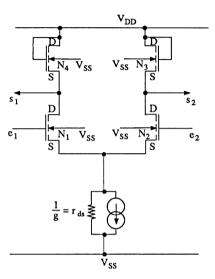

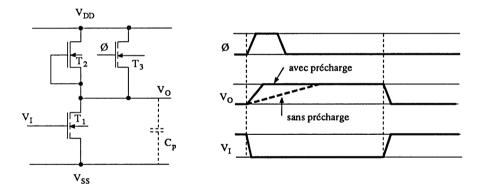

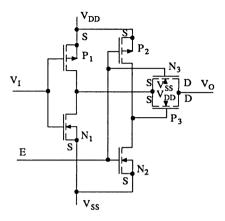

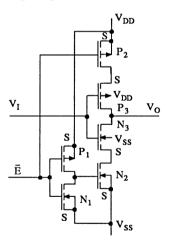

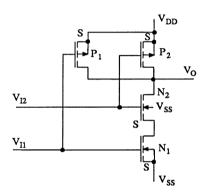

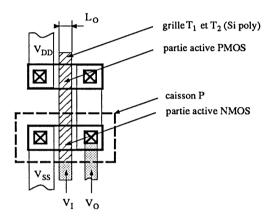

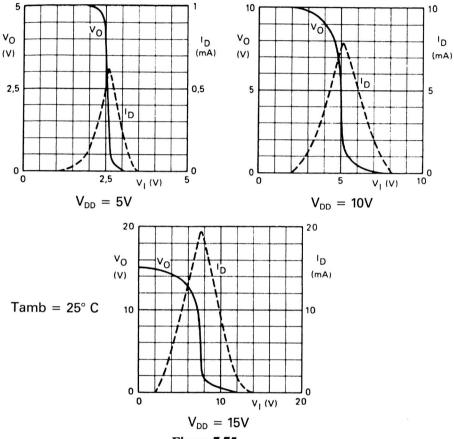

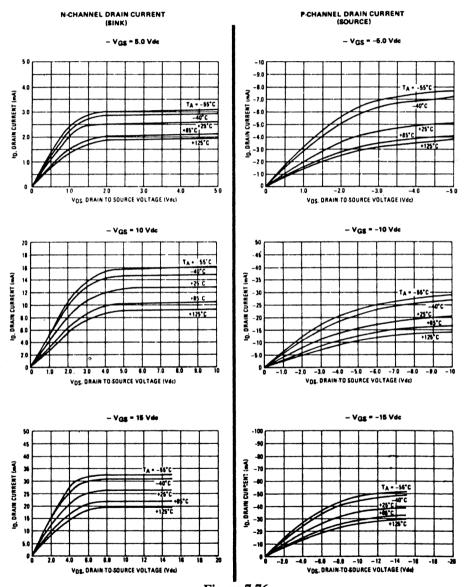

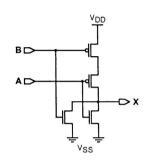

• Famille CMOS (Complementary MOS) utilisant des transistors à enrichissement canal P positionnés vers la ligne positive  $V_{\rm DD}$  de l'alimentation et des transistors à enrichissement canal N positionnés vers la ligne négative  $V_{\rm SS}$  de l'alimentation. La figure 4.4 représente un inverseur CMOS utilisant la symbolisation de la figure 4.1 et deux variantes de symbolisation souvent rencontrées (les flèches des transistors  $T_1$  et  $T_2$  du schéma de droite représentent le sens du courant dans la source, comme en bipolaire, et non la jonction canal-substrat). Cette famille CMOS a trouvé une amélioration technologique dont la dénomination est HCMOS (environ vingt fois plus rapide que la précédente).

• Famille PMOS, symétrique de la famille NMOS, tend à disparaître à cause de la mobilité moindre des trous positifs par rapport à celle des électrons.

#### 4.1.1.4. Domaines d'application des transistors à effet de champ

Les transistors à effet de champ présentent, par rapport aux transistors bipolaires, les avantages suivants :

- très grande impédance d'entrée,

- commande en tension (courant statique de commande très souvent négligeable),

- faible bruit,

- grande rapidité (MESFET),

- distorsions harmonique et d'intermodulation moindres,

- linéarité et symétrie des caractéristiques  $I_D$  ( $V_{DS}$ ) autour de zéro,

- meilleure stabilité thermique,

- pas de second claquage en puissance,

- leur fabrication est plus simple (MOS) et ils prennent moins de place dans les circuits intégrés dont la consommation est très réduite.

Citons toutefois quelques inconvénients:

- plus grande fragilité,

- tenue en tension moindre,

- résistance en conduction et régime de commutation plus élevée...

Les domaines d'application varient suivant le principe.

#### \* Transistors à jonction JFET

#### - Technologie discrète:

- amplification bas niveau à l'aide des montages fondamentaux,

- amplificateurs faible bruit UHF-VHF, ou en audiofréquences,

- amplificateurs micro-ondes avec les transistors MESFET,

- commutation en multiplexage et démultiplexage analogique ou numérique, en modulation et démodulation par « chopper »,

- commande automatique de gain ou CAG dans les amplificateurs, etc.

#### — Technologie intégrée :

• circuits intégrés analogiques (amplificateurs opérationnels BIFET, commutateurs analogiques, etc.).

#### \* Transistors MOSFET à enrichissement

#### - Technologie discrète:

- commutation faible puissance en analogique et numérique, choppers, interface CMOS-TTL, etc.

- commutation forte puissance (VMOS, HEXFET...) en concurrence avec les transistors bipolaires de puissance.

#### — Technologie intégrée :

- circuits intégrés analogiques (amplificateurs opérationnels à faible consommation, commutateurs analogiques, circuits LSI et VLSI, etc.),

- circuits intégrés numériques (logique CMOS, mémoires, circuits VLSI, etc.).

#### \* Transistors MOSFET à appauvrissement

- Technologie discrète:

- amplificateurs basses fréquences, fréquences intermédiaires et VHF,

- · commutateurs analogiques et numériques,

- mélangeurs pour les tuners FM, télévision (MOSFET tétrode ou double grille).

#### — Technologie intégrée :

circuits intégrés VLSI en PMOS ou NMOS (microprocesseurs...). Dans ce cas, les NMOS à appauvrissement sont souvent associés à des NMOS à enrichissement (technologie EDMOS).

#### 4.1.2. TRANSISTORS A JONCTION

#### 4.1.2.1. Jonction *PN*

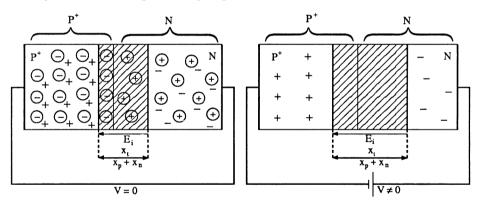

Le transistor à effet de champ à jonction, constitué par exemple d'un canal N, est commandé par une tension appliquée sur une zone  $P^+$ . La présence de la jonction  $P^+N$  (dopage  $P^+ \simeq 10^{18}$  cm<sup>-3</sup> et  $N \simeq 10^{15}$  cm<sup>-3</sup>) impose de rappeler son processus de fontionnement vu aux paragraphes 1.4.2 et 1.4.3. La figure 4.5 présente cette jonction  $P^+N$  non polarisée, puis polarisée en inverse.

Figure 4.5

- Pour V=0, il existe une barrière de potentiel (ou zone de transition ou zone de déplétion) dont la largeur  $x_n$  est plus importante que la largeur  $x_p$ . En effet, la zone neutre s'étend plus du côté le moins dopé (qui est le canal pour le JFET).

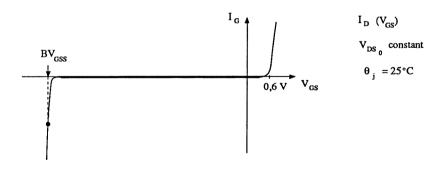

- Pour  $V \neq 0$ , la jonction est polarisée en inverse; la zone de déplétion augmente. C'est ce phénomène qui est utilisé dans les transistors JFET pour diminuer la section du canal, donc la conductance. Notons en plus, qu'il existe un courant inverse constitué de trois composantes :

- un courant de diffusion,

- un courant de génération thermique,

- · un courant de fuite en surface.

et que ce courant global de valeur négligeable à 25°C, augmente très rapidement en fonction de la température (double sensiblement tous les 10°C).

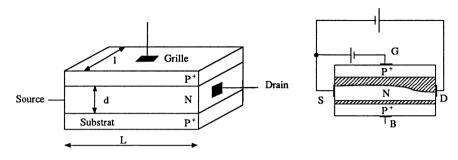

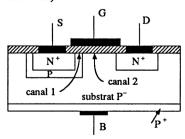

#### 4.1.2.2. Étude qualitative du transistor à jonction JFET canal N

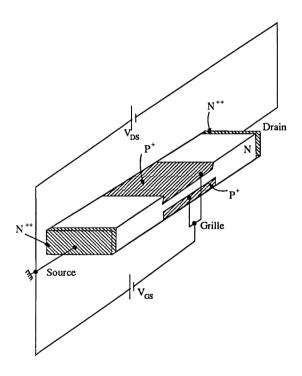

La figure 4.6 représente la perspective d'un transistor JFET simplifié. Le semiconducteur de type N, de forme parallélépipédique, présente à ses extrémités les contacts ohmiques  $N^{++}$  (semiconducteur dégénéré à plus de  $10^{19}$  atomes par cm³ correspondant aux connexions de drain et de source). Deux zones  $P^+$  reliées entre elles constituent la grille de commande (ces deux zones peuvent être indépendantes dans le cas des transistors à double grille). La tension  $V_{\rm DS}$  est positive (conduction d'électrons), alors que  $V_{\rm GS}$  est négative, nulle ou très légèrement positive.

Figure 4.6

L'étude qualitative s'effectue en positionnant, sur différentes figures, la zone de déplétion de la jonction  $P^+N$  dont l'évolution dans le canal dépend de la valeur de  $V_{\rm GS}$  et de  $V_{\rm DS}$ .

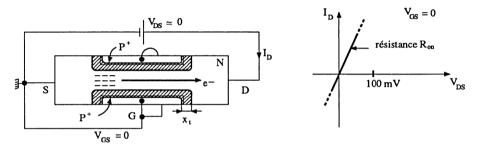

- \* Tension  $V_{\rm DS}$  faible (inférieure à 100 mV), telle qu'elle ne modifie pas la zone de déplétion.

- $-V_{\rm GS}=0$  (figure 4.7). La faible largeur  $x_{\rm t}$  de la zone de déplétion, de la double jonction  $P^+N$  permet la présence d'un canal conducteur dont la résistance est  $R_{\rm DS_{on}}=R_{\rm on}$  (valeur calculée à partir du paragraphe 4.1.1.1. et des éléments du chapitre 1). Cette résistance  $R_{\rm on}$  dépend de la longueur du canal, de sa section active ainsi que de son dopage.

Figure 4.7

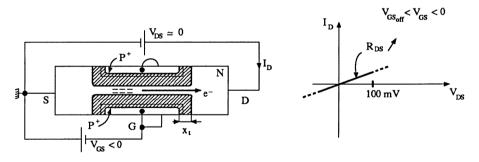

$-V_{\rm GS}$  < 0 et supérieure à  $V_{\rm GSoff}$  (figure 4.8). La présence de la polarisation négative sur la double jonction  $P^+N$  augmente la largeur de transition  $x_{\rm t}$ , diminuant l'épaisseur du canal, donc sa section. La résistance  $R_{\rm DS}$  est ainsi augmentée.

Figure 4.8

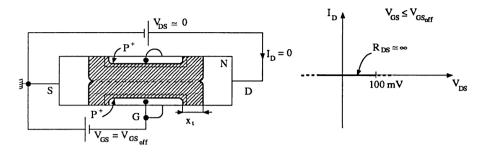

$-V_{\rm GS} \leq V_{\rm GS_{\rm off}}$  (figure 4.9). Cette tension négative  $V_{\rm GS_{\rm off}}$  a augmenté la largeur de la barrière de potentiel  $x_i$  à une valeur telle que le canal est complètement déserté. L'absence de charges libres fait que la résistance  $R_{\rm DS}$  est infinie (si on néglige la présence des charges issues de la création des paires électron-trou).

Figure 4.9

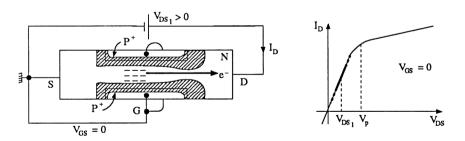

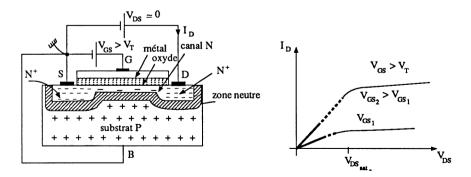

\* Tension  $V_{\rm DS}$  importante. Proposons-nous de représenter la caractéristique  $I_{\rm D}$  ( $V_{\rm DS}$ ) pour  $V_{\rm GS}=0$ . En revenant à la figure 4.7, nous voyons que, pour une tension  $V_{\rm DS}$  très réduite, la zone de déplétion est de largeur constante tout au long du canal (établissement normal de la barrière de potentiel au niveau de la jonction  $P^+N$ ). Le champ électrique créé par la tension  $V_{\rm DS}$  est négligeable et le canal présente une conductance constante  $G_0=\frac{1}{R_{\rm con}}$ .

On augmente la tension  $V_{DS}$ :

—  $V_{\rm DS} < V_{\rm p}$  (figure 4.10). La polarisation de la jonction  $P^+N$  grille-canal est variable selon que nous nous situons vers la source ou vers le drain. Comme  $V_{\rm GS} = 0$  et  $V_{\rm GD} < 0$ , la largeur de la zone de déplétion, côté drain, augmente. Il s'ensuit localement une très légère diminution de la section du canal ne modifiant que très peu sa conductance  $G_{\rm D} = \frac{1}{R_{\rm on}}$ . La caractéristique  $I_{\rm D}$  ( $V_{\rm DS}$ ) est celle d'une résistance ; nous sommes dans la zone linéaire.

Figure 4.10

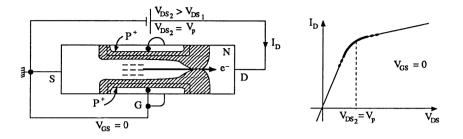

—  $V_{\rm DS} = V_{\rm p}$  (figure 4.11). La tension  $V_{\rm DS}$  continue à augmenter et entraîne, côté drain, une diminution très accentuée de la section du canal jusqu'à son pincement ( $V_{\rm p}$  = tension de pincement). Le courant  $I_{\rm D}$  atteint sa valeur limite, c'est-à-dire sa valeur de saturation ( $I_{\rm Deat}$  pour  $V_{\rm DSat} \simeq V_{\rm p}$  et  $V_{\rm GS} = 0$ ).

Figure 4.11

Remarquons que la tension de pincement  $V_p$  est de même valeur que  $|V_{GS_{off}}|$  (même effet de fermeture du canal) lorsque  $V_{GS} = 0$ .

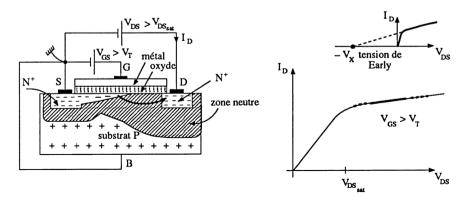

$-V_{\rm DS} > V_{\rm p}$  (figure 4.12). Dans ces conditions, le canal présente une zone complètement déplétée. Tout laisse croire que le courant  $I_{\rm D}$  s'annule. En réalité, les électrons libres du canal sont injectés dans la zone de déplétion puis vers le drain grâce à la présence du champ électrique associé à la tension  $V_{\rm DS}$ . Ce processus de conduction ressemble à celui du transistor bipolaire où les charges issues de l'émetteur traversent la zone neutre de la jonction base-collecteur polarisée en inverse, à cause du champ électrique créé par la tension  $V_{\rm CE}$  (positive pour un NPN).

Figure 4.12

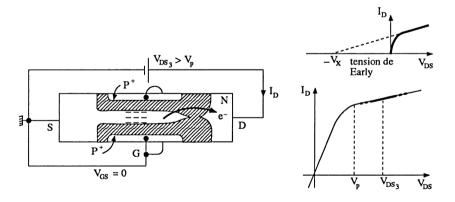

L'augmentation de la tension  $V_{\rm DS}$  au delà de  $V_{\rm p}$  engendre une très légère diminution de la longueur du canal, donc une légère augmentation de sa conductibilité. Ceci entraı̂ne une légère augmentation du courant  $I_{\rm D}$  dont on peut, dans

certains cas, négliger l'existence. Ce phénomène ressemble à l'effet Early pour le transistor bipolaire. La caractéristique  $I_{\rm D}$  ( $V_{\rm DS}$ ) est celle d'un générateur de courant (plus exactement, un récepteur à courant commandé).

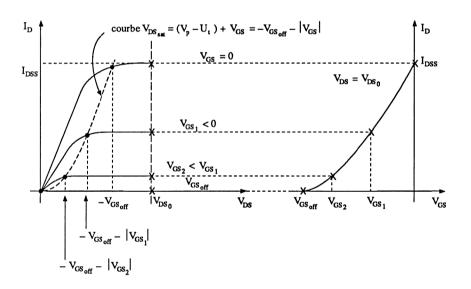

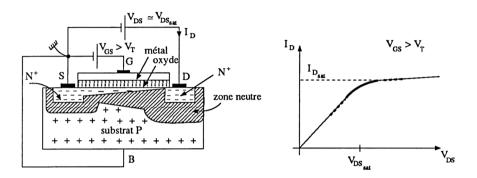

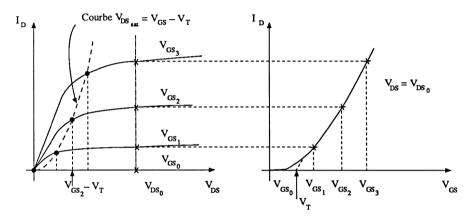

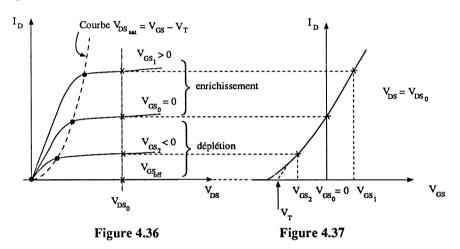

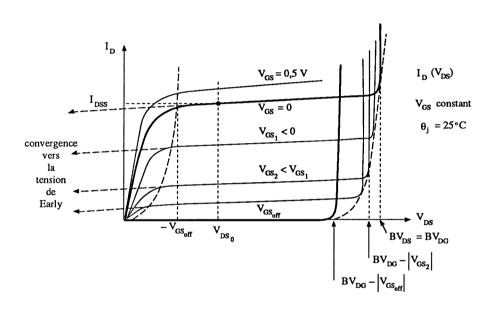

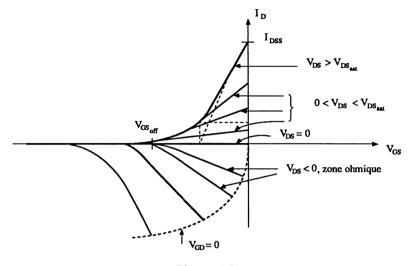

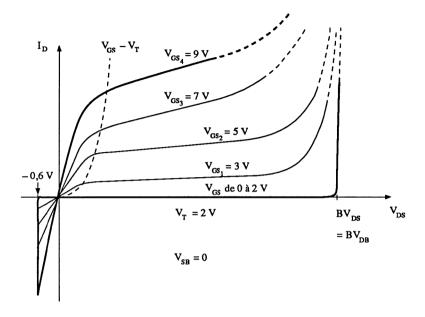

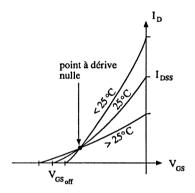

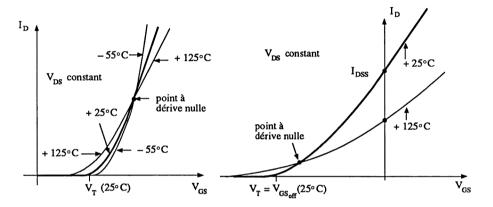

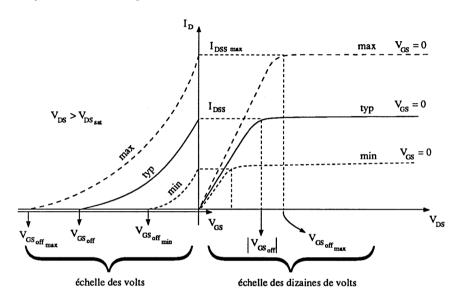

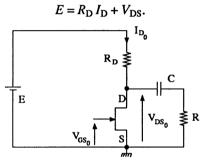

Le raisonnement que nous venons de tenir avec  $V_{\rm GS}=0$  peut être reconduit pour différentes valeurs de  $V_{\rm GS}<0$ . Il est clair qu'une diminution de la section du canal causée par une augmentation de la tension  $|V_{\rm GS}|$  (figures 4.8 et 4.9) a pour conséquence une diminution de la tension de pincement ainsi que l'indiquent les caractéristiques  $I_{\rm D}$  ( $V_{\rm DS}$ ) de la figure 4.13, pour différentes valeurs de  $V_{\rm GS}$ . Pour une tension  $V_{\rm DS}=V_{\rm DS0}$  et supérieure à  $V_{\rm p}$ , on en déduit la caractéristique de transfert  $I_{\rm D}$  ( $V_{\rm GS}$ ) de la figure 4.14. Notons que pour  $V_{\rm GS}=0$ , le courant  $I_{\rm D}$  est égal à  $I_{\rm DSS}$  (Current Drain to Source with Shorted gate).

Figure 4.13

Figure 4.14

#### 4.1.2.3. Étude quantitative du transistor à jonction JFET canal N

En utilisant les éléments de la figure 4.15 (jonction polarisée entre grille et canal, jonction non polarisée entre canal et substrat), nous déduisons les expressions de quelques paramètres du transistor à effet de champ à jonction JFET.

Figure 4.15

— Conduction du canal pour  $V_{\rm GS}=0$  et  $V_{\rm DS}=0$ . Si on néglige l'épaisseur de la zone de déplétion de la double jonction, on obtient la conductance  $G_0$  du canal N appelée conductance métallurgique (statique)

$$G_0 = q N_{\rm D} \mu_{\rm n} \frac{ld}{L} = \frac{1}{R_0} = \sigma \frac{ld}{L}.$$

La valeur de  $R_0$  est proche de celle de  $R_{DS_{on}}$  pour  $V_{GS} = 0$ .

— La tension  $V_{\text{GS} \text{off}}$  correspond à la tension  $V_{\text{GS}}$  obstruant le canal lorsque  $V_{\text{DS}} \simeq 0$  (figure 4.9). Elle est calculée en utilisant l'expression de la largeur de la barrière de potentiel de la jonction  $P^+N$  (entre grille et canal) polarisée en inverse (paragraphe 1.4.3).

$$x_{\rm t} \simeq x_{\rm n} = \sqrt{\frac{2\varepsilon (U_{\rm t} - V_{\rm GS})}{q N_{\rm D}}}$$

avec  $V_{\rm GS} < 0$

où  $U_t$  représente le potentiel de diffusion de la jonction  $P^+N$

$$U_{\rm t} = \frac{kT}{q} \ln \frac{N_{\rm D} N_{\rm A}}{n_{\rm i}^2}.$$

Comme le canal est obstrué lorsque  $x_t = d$  pour  $V_{GS} = V_{GS_{off}}$  et que l'influence du substrat, dans notre cas, est négligeable, il vient

$$V_{\text{GS}_{\text{off}}} = -\frac{q N_{\text{D}} d^2}{2\varepsilon} + U_{\text{t}} = -V_{\text{p}} + U_{\text{t}}$$

$$V_{\text{p}} = \frac{q N_{\text{D}} d^2}{2\varepsilon}.$$

avec

Remarquons que si le substrat est au même potentiel que celui de la grille, la tension de blocage  $V_{\rm GSoff}$  est divisée par 2.

— La conduction du canal dépend de  $V_{\rm DS}$  et de  $V_{\rm GS}$ . On déduit l'expression du courant  $I_{\rm D}$ , jusqu'au pincement, à partir d'un calcul intégral non précisé

$$I_{\rm D} = G_0 \left\{ V_{\rm DS} - \frac{2}{3} \sqrt{\frac{2\varepsilon}{q N_{\rm D} d^2}} \left[ (U_{\rm t} - V_{\rm GS} + V_{\rm DS})^{\frac{3}{2}} - (U_{\rm t} - V_{\rm GS})^{\frac{3}{2}} \right] \right\}$$

ou encore

$$I_{\rm D} = G_0 \left\{ V_{\rm DS} - \frac{2}{3\sqrt{V_{\rm p}}} \left[ (U_{\rm t} - V_{\rm GS} + V_{\rm DS})^{\frac{3}{2}} - (U_{\rm t} - V_{\rm GS})^{\frac{3}{2}} \right] \right\}$$

#### • Zone ohmique des caractéristiques $I_D(V_{DS})$ .

Pour  $V_{DS} < (U_t - V_{GS})$ , l'expression précédente du courant  $I_D$  en fonction de la tension  $V_{DS}$  devient

$I_{\rm D} = G_0 \left[ 1 - \sqrt{\frac{2\varepsilon}{q N_{\rm D} d^2} (U_{\rm t} - V_{\rm GS})} \right] V_{\rm DS}$

ou encore

$$I_{\rm D} = G_0 \left[ 1 - \sqrt{\frac{U_{\rm r} - V_{\rm GS}}{V_{\rm p}}} \right] \ V_{\rm DS}. \label{eq:ID}$$

Cette expression laisse apparaître la relation linéaire  $I_D = G'_0 V_{DS}$  correspondant à des droites passant par l'origine. Le transistor JFET est équivalent à une résistance commandée  $R'_0 (V_{GS}) = R_{DSon} (V_{GS})$ .

De la relation précédente, nous vérifions que pour  $U_{\rm t}-V_{\rm GS}=V_{\rm p}$ , le courant  $I_{\rm D}$  s'annule et nous retrouvons la relation

$$V_{\text{GS}_{\text{off}}} = U_{\text{t}} - V_{\text{p}}.$$

#### • Zone de saturation des caractéristiques $I_D$ ( $V_{DS}$ ).

L'apparition du pincement du canal pour  $V_{GS}$  et  $V_{DS}$  non nulles a lieu lorsque  $V_{DS} = V_{DS_{sat}}$ , soit

$$V_{\rm DS_{sat}} = (V_{\rm p} - U_{\rm t}) + V_{\rm GS}$$

$(V_{\rm GS} < 0)$ .

Lorsque  $V_{GS} = 0$ ,  $V_{DS_{sat}} = V_p - U_t$ .

Remarquons que dans le cas où le potentiel de diffusion  $U_{\rm t}$  est négligeable, nous avons

et

$$\begin{split} V_{\rm p} &= -V_{\rm GSoff} \\ V_{\rm DS_{\rm sat}} &= V_{\rm p} + V_{\rm GS} = V_{\rm p} - \mid V_{\rm GS} \mid . \end{split}$$

A cette tension de saturation  $V_{\mathrm{DS_{sat}}}$  correspond un courant

$$I_{\rm D_{Sat}} = + \frac{l \, \mu_{\rm n} \, q^2 \, N_{\rm d}^2 \, d^3}{6 \, \varepsilon \, L} \left[ 1 - 3 \, \left( 1 - \frac{V_{\rm DS_{sat}}}{V_{\rm p}} \right) + 2 \, \left( 1 - \frac{V_{\rm DS_{sat}}}{V_{\rm p}} \right)^{\frac{3}{2}} \right].$$

Ces relations traduisent la courbe en pointillé de la figure 4.13 (lieu des coudes) et permettent de déterminer la transconductance  $g = \frac{\mathrm{d} I_\mathrm{D}}{\mathrm{d} V_\mathrm{GS}}$  pour  $V_\mathrm{DS} \ge V_\mathrm{DS_{sat}}$  (en négligeant l'effet Early)

$$g_{\rm fs} = \frac{\mathrm{d} I_{\rm D_{\rm sat}}}{\mathrm{d} V_{\rm GS}} = G_0 \left[ 1 - \frac{\sqrt{U_{\rm t} - V_{\rm GS}}}{V_{\rm p}} \right]$$

en siemens S

#### Remarques

- $g_{\rm fs}$  représente la transconductance directe en source commune.

- La qualité d'un transistor à effet de champ à jonction est associée à sa transconductance  $g_{fs}$  donc à  $G_0$ , ou encore à la mobilité des porteurs dont la vitesse atteint sa limite à la saturation.

- Il ne faut pas confondre la conductance statique du canal  $G_0 = \frac{1}{R_{\rm DS_{on}}} = \frac{I_{\rm D}}{V_{\rm DS}}$  utilisée dans la zone résistive des caractéristiques de sortie, la conductance dynamique de sortie  $g_{\rm os} = \frac{{\rm d} I_{\rm D_{sat}}}{{\rm d} V_{\rm DS}}$  et la transconductance dynamique  $g_{\rm fs} = \frac{{\rm d} I_{\rm D_{sat}}}{{\rm d} V_{\rm GS}}$  utilisée dans la zone de saturation.

- Dans notre cas d'étude, nous avons  $G_0' = g_{\rm fs}$  car nous avons supposé que la caractéristique  $I_{\rm D}$  ( $V_{\rm DS}$  et  $V_{\rm GS}$ ) était linéaire jusqu'à la saturation.

- Nous n'avons pas tenu compte des résistances parasites r existant entre le canal et les connexions de drain et de source. En réalité, la résistance  $R_{\rm DS_{on}}$  devient  $R_{\rm DS_{on}} + r$  et la transconductance maximale s'écrit  $g'_{\rm fs_0} = \frac{g_{\rm fs}}{1 + r \, g_{\rm fs}}$ .

#### 4.1.2.4. Relations simplifiées associées au transistor JFET

Expérimentalement, on déduit la valeur approchée des paramètres pour un transistor dont le substrat est relié à la source (deux zones obstruant le canal).

— Le courant de saturation  $I_{DSS} = I_{D_{Sat}}$  pour  $V_{GS} = 0$  est approximé par la relation

$I_{\text{DSS}} \simeq \frac{|V_{\text{GS}_{\text{off}}}|}{3 R_{\text{DS}_{\text{on}}}}$  $V_{\text{GS}_{\text{off}}} = -V_{\text{p}} + U_{\text{t}}.$

avec

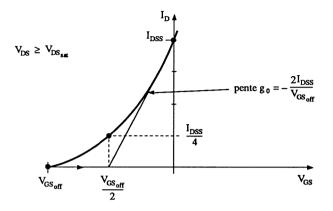

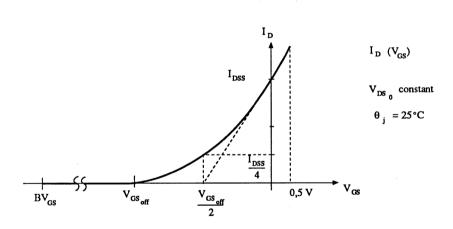

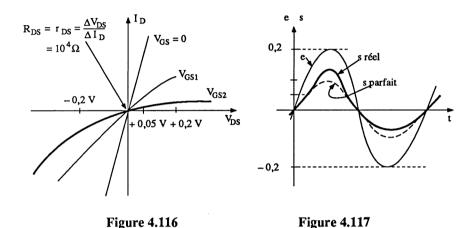

— Pour  $V_{\rm DS} \ge V_{\rm DS_{sat}}$ , le courant de saturation  $I_{\rm D_{sat}}$  est fonction de la valeur de  $V_{\rm GS}$  (figure 4.14). La lourdeur des expressions précédentes nous autorise à utiliser l'approximation parabolique, très souvent suffisante

$$I_{\mathrm{D_{Sat}}} \simeq I_{\mathrm{DSS}} \left( 1 - \frac{V_{\mathrm{GS}}}{V_{\mathrm{GS_{off}}}} \right)^{2} \quad \begin{cases} V_{\mathrm{GS}} \leq 0 \\ V_{\mathrm{GS_{off}}} < 0 \end{cases}$$

La figure 4.16 représente le graphe de cette fonction mathématique facile à tracer, en utilisant les trois points

$$I_{\rm D} = I_{\rm DSS}$$

pour  $V_{\rm GS} = 0$

$$I_{\rm D} = \frac{I_{\rm DSS}}{4}$$

pour  $V_{\rm GS} = \frac{V_{\rm GS\,off}}{2}$

$$I_{\rm D} = 0$$

pour  $V_{\rm GS} = V_{\rm GS\,off}$

Figure 4.16

La dérivée de cette fonction représente la pente, donc la transconductance, du transistor JFET

$$g = g_{fs} = \frac{\mathrm{d}I_{D_{sat}}}{\mathrm{d}V_{GS}} = \frac{\mathrm{d}}{\mathrm{d}V_{GS}} \left[ I_{DSS} \left( 1 - \frac{2V_{GS}}{V_{GS_{off}}} + \frac{V_{GS}^2}{V_{GS_{off}}} \right) \right]$$

$$g = g_{fs} = -\frac{2I_{DSS}}{V_{GS_{off}}} \left( 1 - \frac{V_{GS}}{V_{GS_{off}}} \right) \qquad \text{en siemens S}$$

$$S = A/V$$

soit

Pour  $V_{GS} = 0$ , nous avons la pente maximale  $g_0$  (en excluant la possibilité d'une faible tension  $V_{GS}$  positive)

$$g_0 = g_{fs0} = -\frac{I_{DSS}}{V_{GSoff}/2}.$$

Nous en déduisons une nouvelle expression de la pente

$$g = g_{\rm fs} = g_{\rm fs0} \left( 1 - \frac{V_{\rm GS}}{V_{\rm GS_{\rm off}}} \right) = g_0 \left( 1 - \frac{V_{\rm GS}}{V_{\rm GS_{\rm off}}} \right).$$

Remarquons que cette relation fournit aux limites

$$g = g_{fs} = g_{fs0} = g_0$$

pour  $I_D = I_{DSS}$  et  $V_{GS} = 0$

$g = g_{fs} = 0$  pour  $I_D = 0$  et  $V_{GS} = V_{GSoff}$

#### 4.1.3. TRANSISTORS A GRILLE ISOLÉE MOSFET

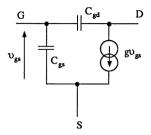

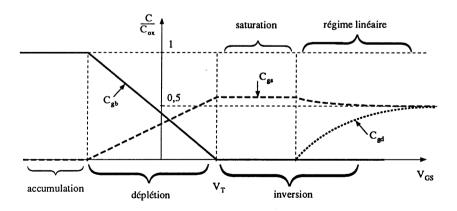

Les transistors à grille isolée MOSFET fonctionnent suivant un principe tout à fait différent de celui du transistor JFET. Ils utilisent le phénomène des charges stockées sur les « armatures » d'un condensateur plan. Il est donc nécessaire, dans un premier temps, d'étudier le comportement du condensateur MOS.

#### 4.1.3.1. Condensateur métal-oxyde-semiconducteur\*

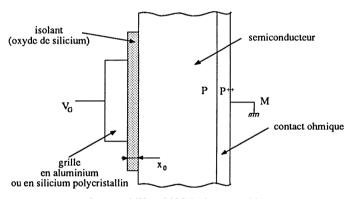

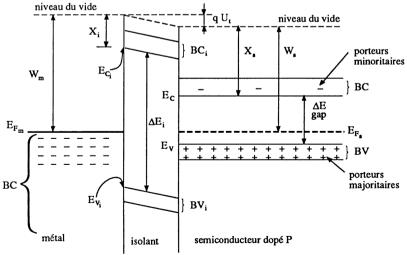

L'étude du condensateur MOS (Métal-Oxyde-Semiconducteur) ou plus généralement MIS (Métal-Isolant-Semiconducteur) est analogue à celle des condensateurs plans. La différence essentielle est que, dans la structure MOS (où l'oxyde de silicium est un très bon isolant), les charges stockées du côté du semiconducteur occupent un volume alors que celles stockées du côté du métal, occupent la surface de contact.

Nous considérons le condensateur MOS de la figure 4.17 avec, comme conditions :

- une épaisseur d'isolant  $x_0$  de 10 à 100 nm telle qu'une faible tension  $V_{\rm GM} = V_{\rm G}$  fournisse un fort champ électrique, permettant le déplacement des charges dans le matériau semiconducteur (courbure des bandes de valence et de conduction),

- un matériau semiconducteur dopé P (en général  $10^{15}$  à  $10^{16}$  cm<sup>-3</sup>),

- un contact ohmique  $P^{++}$  (supérieur à  $10^{19}$  cm<sup>-3</sup>).

Structure MIS ou MOS (isolant = oxyde)

Figure 4.17

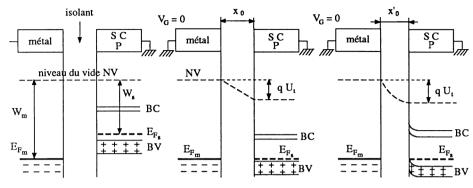

A. Sans polarisation, le diagramme d'énergie est celui de la figure 4.18 (pour comprendre ce diagramme, il faut revenir au chapitre 2.4.2 traitant la barrière Schottky, et plus particulièrement, à la figure 2.115). Par rapport au niveau du vide, le métal présente un travail de sortie  $W_{\rm m}$  et le semiconducteur, un travail de sortie  $W_{\rm s}$  égal ou différent du précédent.

<sup>\*</sup> Pour plus de détails, il faut consulter les ouvrages traitant la physique des semiconducteurs, cités en bibliographie.

Figure 4.18

- Lorsque ces deux matériaux ne sont pas reliés, ils sont énergiquement indépendants.

- Dans le cas où on les relie ( $V_G = 0$ ), nous sommes en présence d'un seul système thermodynamique. Alors, les niveaux de Fermi s'alignent :

- Si l'épaisseur  $x_0$  de l'isolant est suffisamment importante, les bandes de conduction BC et de valence BV du semiconducteur sont plates.

- Si l'épaisseur  $x_0$  diminue et devient  $x'_0$ , les bandes s'incurvent.

- Si  $x_0 = 0$ , nous sommes en présence du contact Schottky de la figure 2.115.

La figure 4.19 représente le diagramme d'énergie détaillé pour  $V_G = 0$ , dans l'hypothèse des bandes plates. La différence de potentiel de contact q  $U_t$  qui apparaît est analogue à la tension de diffusion de la jonction PN avec, comme relation

$$q U_{t} = W_{m} - W_{s}.$$

**Figure 4.19**

Il est évident qu'une capacité MOS est réalisée à partir de matériaux sélectionnés, de manière à obtenir une valeur q  $U_t$  bien particulière. C'est pour cela qu'en technologie silicium, l'isolant, sauf cas particulier, est de l'oxyde de silicium et le métal, de l'aluminium et plus couramment du silicium polycristallin dont la tenue en température, lors de la fabrication, est meilleure que celle de l'aluminium. Notons que le silicium polycristallin ou polysilicium est du silicium dopé de façon aléatoire et se comporte comme un métal. A ce titre, nous donnons quelques valeurs associées à la figure 4.19:

- travail de sortie de l'aluminium  $W_{\rm m} = 4.3 \text{ eV}$ ,

- affinité du silicium  $X_s = 4.01 \text{ eV}$ ,

- gap du silicium  $\Delta E = E_C E_V = 1,12 \text{ eV}$ ,

- affinité électronique de l'oxyde de silicium  $x_i = 0.9$  eV,

- gap de l'oxyde de silicium  $\Delta E_i = E_{C_i} E_{V_i} = 8,1 \text{ eV}.$

Le travail de sortie  $W_s$  du silicium est calculé à partir de la différence  $E_C - E_{F_s}$  (voir chapitre 1 et exercices de fin de section).

### B. Avec polarisation $V_G \neq 0$ , if y a lieu de considérer plusieurs cas.

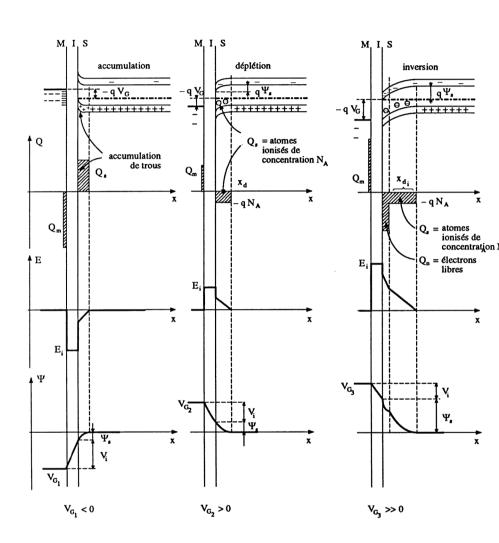

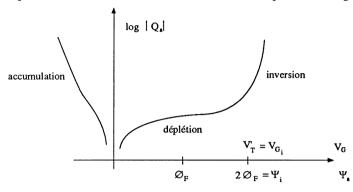

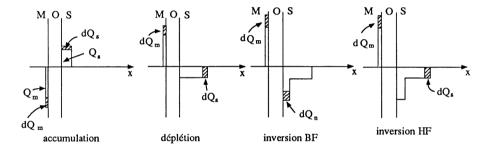

— Régime d'accumulation (figure 4.20). On polarise la grille par une tension négative  $V_{\rm G_1}$ . La présence du champ électrique tend à attirer les porteurs majoritaires libres du semiconducteur P vers l'interface oxyde-semiconducteur. Il y a alors, dans cette zone, une charge d'espace positive associée à une accumulation de trous.

La charge positive totale  $Q_{\rm s}$ , dans l'interface oxyde-semiconducteur est équilibrée par la charge négative totale  $Q_{\rm m}$  située à la surface du métal.

Le champ électrique  $E_i$ , à l'intérieur de l'isolant, est constant (absence de charges dans celui-ci), puis décroît linéairement dans le semiconducteur, à cause de la densité uniforme des charges positives.

Le potentiel  $\psi$  obtenu après intégration du champ électrique E nous fournit la tension  $V_G$  appliquée à la grille. Cette tension représente la somme de la ddp  $V_i$  aux bornes de l'isolant et de la ddp  $\psi_s$  interne au semiconducteur, appelée potentiel de surface et traduisant la courbure des bandes.

Ces grandeurs sont associées quantitativement par les relations

$$Q_{\rm m} = -Q_{\rm s}$$

$$V_{\rm G_1} = V_{\rm i} + \psi_{\rm s}$$

$$V_{\rm i} = \frac{Q_{\rm m}}{C_{\rm i}} = -\frac{Q_{\rm s}}{C_{\rm i}}$$

avec

où  $C_i = \frac{\varepsilon_i \ \varepsilon_0}{x_0}$  représente la capacité par unité de surface de l'isolant.

— Régime de déplétion ou de désertion (figure 4.21). La faible polarisation positive  $V_{\rm G2}$  chasse quelques trous de l'interface oxyde-semiconducteur créant une

Figure 4.20

Figure 4.21

Figure 4.22

charge d'espace négative dans ce demier, correspondant aux atomes d'impuretés ionisés. Les relations précédentes deviennent :

$$\begin{aligned} Q_{\rm m} &= -Q_{\rm s} = q \, N_{\rm A} \, x_{\rm d} \\ V_{\rm G_2} &= V_{\rm i} + \psi_{\rm s} \\ V_{\rm i} &= \frac{Q_{\rm m}}{C_{\rm i}} = \frac{q \, N_{\rm A} \, x_{\rm d}}{C_{\rm i}} \\ \psi_{\rm s} &= \frac{q \, N_{\rm A} \, x_{\rm d}^2}{2 \, \varepsilon_{\rm r} \, \varepsilon_0} \qquad (\varepsilon = \varepsilon_{\rm r} \, \varepsilon_0 \simeq 10^{10} \, \rm pour \, Si). \end{aligned}$$

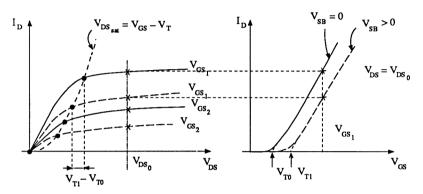

— Régime d'inversion (figure 4.22). Lorsque la polarisation  $V_{\rm G3}$  devient très positive, on atteint une répulsion de trous et une attraction des électrons minoritaires du matériau semiconducteur dopé P. La concentration en électrons libres devient supérieure à la concentration en trous. Dans ces conditions, la courbure des bandes est telle que le niveau de Fermi  $E_{\rm Fs}$  est plus proche de  $E_{\rm C}$  en surface que de  $E_{\rm V}$  en volume. La couche d'inversion de charge  $Q_{\rm n}$  constituée d'électrons libres est séparée du semiconducteur P par une région déserte constituée d'atomes ionisés  $N_{\rm A}$  de charge -q  $N_{\rm A}$   $x_{\rm di}$ . On en déduit la relation

$$Q_{\rm m} = -Q_{\rm s} = -Q_{\rm n} + q N_{\rm A} x_{\rm di}.$$

Le seuil d'inversion correspond à l'égalité

$$n_s = N_A$$

$$\begin{cases} n_s, \text{ nombre d'électrons minoritaires} \\ N_A, \text{ concentration de dopage} \end{cases}$$

(Nous avons vu, dans le chapitre 1, la manière de déterminer  $n_s$ .)

A ce seuil d'inversion correspond un potentiel

$$\psi_{i} = \frac{2kT}{q} \ln \frac{N_{A}}{n_{i}}$$

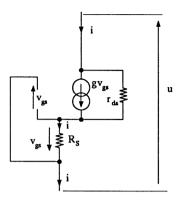

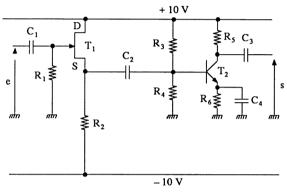

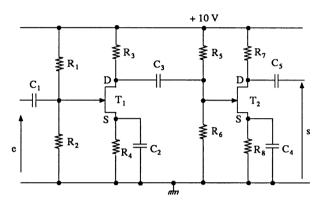

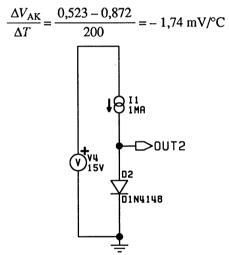

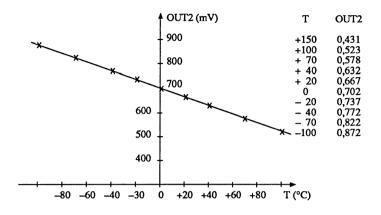

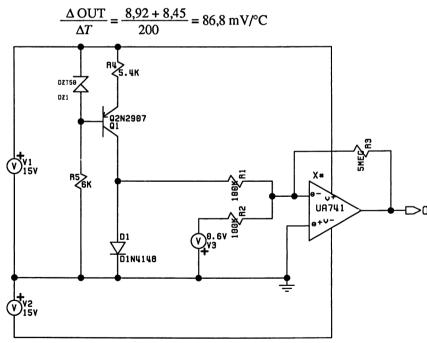

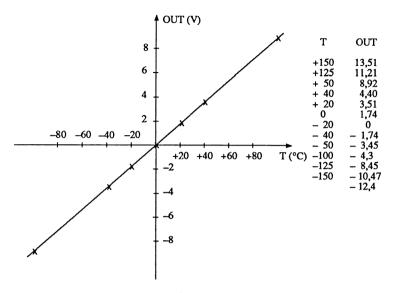

et une épaisseur de la zone déserte